## Analysen und Methoden optimierender Compiler zur Steigerung der Effizienz von Speicherzugriffen in eingebetteten Systemen

Björn Franke

Dortmund, 30. August 1999

## Inhaltsverzeichnis

| 1 | Ein | leitung                                     | 10 |

|---|-----|---------------------------------------------|----|

|   | 1.1 | Ziele der Diplomarbeit                      | 11 |

|   | 1.2 | Überblick                                   | 14 |

| 2 | DSI | P-Architekturen                             | 15 |

|   | 2.1 | Registersätze                               | 16 |

|   |     | 2.1.1 Heterogene Registersätze              | 16 |

|   |     | 2.1.2 Homogene Registersätze                | 17 |

|   | 2.2 | Address Generation Unit                     | 18 |

|   | 2.3 | Speicherorganisation und On-Chip-RAM        | 21 |

|   | 2.4 | Weitere Literatur                           | 23 |

| 3 | Dat | enabhängigkeit, Analysen, Optimierungen     | 24 |

|   | 3.1 | Grundlegende Begriffe                       | 24 |

|   | 3.2 | Abhängigkeitsrelationen                     | 27 |

|   | 3.3 | Datenabhängigkeitsanalysen                  | 29 |

|   |     | 3.3.1 Datenflußverbände                     | 31 |

|   |     | 3.3.2 Transferfunktionen                    | 32 |

|   |     | 3.3.3 Iterative Datenflußanalyse            | 39 |

|   |     | 3.3.4 Konkrete Datenflußprobleme            | 41 |

|   | 3.4 | Skalare Optimierungen                       | 42 |

|   |     | 3.4.1 Klassifikation der Codeverbesserungen | 43 |

|   |     | 3.4.2          | Wechselbeziehungen                                       | 44 |

|---|-----|----------------|----------------------------------------------------------|----|

|   | 3.5 | Static         | Single-Assignment (SSA) Form                             | 46 |

| 4 | Dat | enfluß         | analysen für Arrays                                      | 48 |

|   | 4.1 | Grund          | llagen zur Array-Datenflußanalyse                        | 49 |

|   |     | 4.1.1          | Problemeinschränkung vs. Approximationslösung            | 50 |

|   |     | 4.1.2          | Begriffe                                                 | 52 |

|   | 4.2 | $\delta$ -Verf | ahren zur Array-Datenflußanalyse                         | 55 |

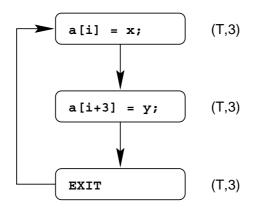

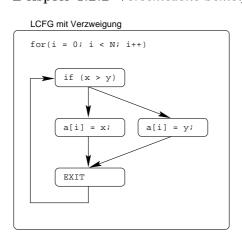

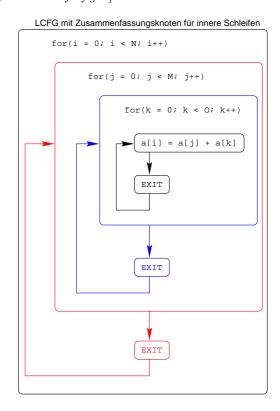

|   |     | 4.2.1          | Schleifenkontrollflußgraph                               | 58 |

|   |     | 4.2.2          | Verwendeter Datenflußverband und Operatoren              | 59 |

|   |     | 4.2.3          | Transferfunktionen                                       | 60 |

|   |     | 4.2.4          | Datenfluß-Gleichungssystem und iterative Fixpunkt-Lösung | 67 |

|   |     | 4.2.5          | Möglichkeiten zur Parametrisierung                       | 69 |

|   |     | 4.2.6          | Behandlung mehrdimensionaler Arrays und Loop Nests .     | 71 |

|   |     | 4.2.7          | Ermöglichte Optimierungen                                | 73 |

|   |     | 4.2.8          | Vor- und Nachteile                                       | 74 |

|   | 4.3 | Stretc.        | hed-Loop-Array-Datenflußanalyse                          | 74 |

|   |     | 4.3.1          | Voraussetzungen                                          | 75 |

|   |     | 4.3.2          | Verfahrensüberblick                                      | 75 |

|   |     | 4.3.3          | Verwendeter Datenflußverband und Operatoren              | 79 |

|   |     | 4.3.4          | Bestimmung von G und K                                   | 80 |

|   |     | 4.3.5          | Transferfunktionen                                       | 82 |

|   |     | 4.3.6          | Datenflußanalyse                                         | 83 |

|   |     | 4.3.7          | Parametrisierung                                         | 88 |

|   |     | 4.3.8          | Ermöglichte Optimierungen                                | 89 |

|   |     | 4.3.9          | Vor- und Nachteile                                       | 89 |

|   | 4.4 | Lazy-          | Verfahren zur Array-Datenflußanalyse                     | 90 |

|   |     | 4.4.1          | Voraussetzungen                                          | 90 |

|   |     | 4.4.2           | Definitionen und Notation                                         | 90  |

|---|-----|-----------------|-------------------------------------------------------------------|-----|

|   |     | 4.4.3           | Darstellung von Datenabhängigkeiten                               | 92  |

|   |     | 4.4.4           | Abhängigkeitsrelationen                                           | 93  |

|   |     | 4.4.5           | Algorithmus zur Lazy-Array-Datenflußanalyse                       | 94  |

|   |     | 4.4.6           | Erweiterungen zur Behandlung nicht-affiner Programm-<br>fragmente | 96  |

|   |     | 4.4.7           | Vor- und Nachteile                                                | 100 |

|   | 4.5 | DSA-V           | Verfahren zur Array-Datenflußanalyse                              | 101 |

|   |     | 4.5.1           | Dynamic Single Assignment                                         | 102 |

|   |     | 4.5.2           | DSA-Datenflußanalyse                                              | 105 |

|   |     | 4.5.3           | Anpassung                                                         | 109 |

|   |     | 4.5.4           | Ermöglichte Optimierungen                                         | 110 |

|   |     | 4.5.5           | Vor- und Nachteile                                                | 110 |

|   | 4.6 | Vergle          | ich und Bewertung der Array-Datenflußanalysen                     | 111 |

|   | 4.7 | Weiter          | re Literatur                                                      | 115 |

| 5 | Loa | $_{ m id/Stor}$ | e-Optimierungen                                                   | 118 |

|   | 5.1 | Elimin          | nation redundanter Stores                                         | 119 |

|   |     | 5.1.1           | Analyse                                                           | 123 |

|   |     | 5.1.2           | Interpretation der Analyse                                        | 124 |

|   |     | 5.1.3           | Optimierung                                                       | 124 |

|   |     | 5.1.4           | Vor- und Nachteile von RSE                                        | 126 |

|   | 5.2 | Elimin          | ation redundanter Loads                                           | 129 |

|   |     | 5.2.1           | Analyse                                                           | 130 |

|   |     | 5.2.2           | Interpretation der Analyse                                        | 131 |

|   |     | 5.2.3           | Optimierung                                                       | 131 |

|   |     | 5.2.4           | Vor- und Nachteile der RLE                                        | 132 |

|   | 5.3 | Einfac          | hes Register-Pipelining                                           | 134 |

|   |     | 5.3.1           | Analyse und deren Interpretation                                  | 135 |

|   |     | 5.3.2    | Optimierung                                                 | 5   |

|---|-----|----------|-------------------------------------------------------------|-----|

|   |     | 5.3.3    | Vor- und Nachteile                                          | 7   |

|   | 5.4 | Erwei    | terte Möglichkeiten                                         | 0   |

|   |     | 5.4.1    | Weitere Fälle zur RLE                                       | 0   |

|   |     | 5.4.2    | Behandlung mehrdimensionaler Arrays und Loop Nests . 14     | 2   |

|   | 5.5 | Beurte   | eilung der verschiedenen Optimierungen                      | 5   |

| 6 | Erw | eiterte  | e Load/Store-Optimierungen 14                               | 7   |

|   | 6.1 | Verbe    | ssertes Register-Pipelining                                 | :7  |

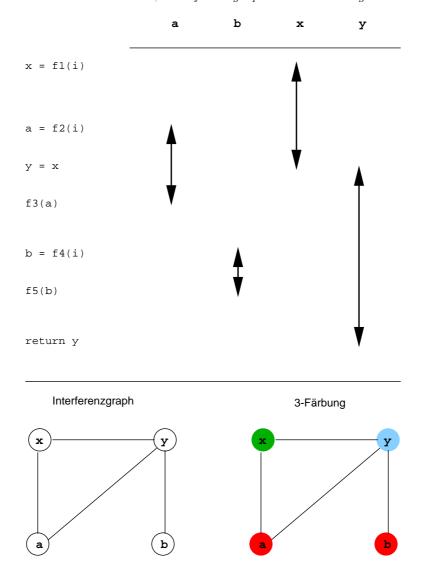

|   |     | 6.1.1    | Integrierter Interferenzgraph und dessen Färbung 14         | 9   |

|   | 6.2 | Optim    | ales Register-Pipelining                                    | 0   |

|   |     | 6.2.1    | Algorithmus                                                 | 1   |

|   |     | 6.2.2    | Vor- und Nachteile                                          | 7   |

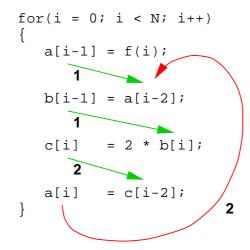

|   | 6.3 | RP m     | it Einsatz der AGU und Verwendung von On-Chip-RAM $$ . 15   | 8   |

|   |     | 6.3.1    | Vor- und Nachteile                                          | 0   |

|   | 6.4 | Beurte   | eilung der verschiedenen Optimierungen                      | 2   |

|   | 6.5 | Weiter   | re Literatur                                                | 3   |

| 7 | Spe | zielle ( | Optimierungen 16                                            | 4   |

|   | 7.1 | Kontr    | olliertes Loop Unrolling                                    | 5   |

|   |     | 7.1.1    | Vor- und Nachteile                                          | 7   |

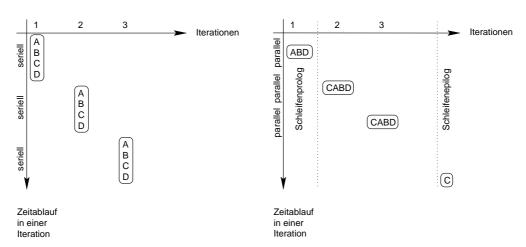

|   | 7.2 | Unters   | stützung von Software-Pipelining                            | 8   |

|   |     | 7.2.1    | Vor- und Nachteile                                          | 0   |

|   | 7.3 | Aggre    | gate Array Computations                                     | 0   |

|   |     | 7.3.1    | Erkennung von AACs                                          | 1   |

|   |     | 7.3.2    | Transformation von AACs in inkrementalisierte Darstellungen | 3   |

|   |     | 7.3.3    | Erzeugung neuer Programmschleifen                           | 5   |

|   |     | 7.3.4    | Weitere Möglichkeiten                                       | 6   |

|   |     | 7 2 5    | Vor. und Nachtaila                                          | · 6 |

|    | 7.4        | Beurte                                          | eilung der verschiedenen Optimierungen             | 177                                           |

|----|------------|-------------------------------------------------|----------------------------------------------------|-----------------------------------------------|

|    | 7.5        | Weiter                                          | e Literatur                                        | 178                                           |

| 8  | Ver        | suche                                           | und empirische Resultate 1                         | 79                                            |

|    | 8.1        | Imple                                           | mentierte Datenflußanalysen und Optimierungen      | 179                                           |

|    | 8.2        | Versuo                                          | che und Versuchsziele                              | 179                                           |

|    | 8.3        | Versuo                                          | chsbeobachtungen und Resultate                     | 181                                           |

|    |            | 8.3.1                                           | Gemischte einfache Referenzen                      | 181                                           |

|    |            | 8.3.2                                           | Gemischte komplexe Referenzen                      | 183                                           |

|    |            | 8.3.3                                           | Variation der Abhängigkeitsdistanzen               | 184                                           |

|    |            | 8.3.4                                           | Verschiedene Optimierungsstufen                    | 188                                           |

|    |            | 8.3.5                                           | Gegenbeispiele                                     | 192                                           |

|    | 8.4        | Bewer                                           | tungen                                             | 194                                           |

| 9  | Kon        | ıklusio                                         | nen und Ausblick 1                                 | .96                                           |

|    |            |                                                 |                                                    |                                               |

| Li | terat      | urverz                                          | zeichnis 2                                         | 201                                           |

|    |            |                                                 |                                                    | 201<br>204                                    |

|    |            | ument                                           |                                                    | 204                                           |

|    | Dok        | ument                                           | tation der Implementation 2                        | <b>204</b><br>204                             |

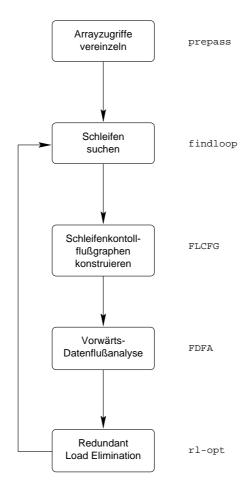

|    | Dok        | Redun                                           | tation der Implementation 2  dant Load Elimination | <b>204</b><br>204                             |

|    | Dok        | Redun                                           | tation der Implementation 2  dant Load Elimination | 204<br>204<br>205<br>205                      |

|    | Dok        | Redun<br>A.1.1<br>A.1.2                         | tation der Implementation 2 dant Load Elimination  | 204<br>204<br>205<br>205<br>206               |

|    | Dok        | Redun A.1.1 A.1.2 A.1.3                         | tation der Implementation 2  dant Load Elimination | 204<br>205<br>205<br>206<br>206               |

|    | Dok        | Redun A.1.1 A.1.2 A.1.3 A.1.4 A.1.5             | tation der Implementation 2 dant Load Elimination  | 204<br>204<br>2205<br>2206<br>2206<br>2209    |

|    | Dok<br>A.1 | Redun A.1.1 A.1.2 A.1.3 A.1.4 A.1.5             | tation der Implementation 2 dant Load Elimination  | 204<br>205<br>205<br>206<br>206<br>209<br>210 |

|    | Dok<br>A.1 | Redun A.1.1 A.1.2 A.1.3 A.1.4 A.1.5 Redun       | tation der Implementation 2  dant Load Elimination | 204<br>205<br>205<br>206<br>206<br>209<br>210 |

|    | Dok<br>A.1 | Redun A.1.1 A.1.2 A.1.3 A.1.4 A.1.5 Redun A.2.1 | tation der Implementation 2  dant Load Elimination | 204<br>205<br>205<br>206<br>209<br>210<br>210 |

| INHALTSVI | ERZEICHNIS |

|-----------|------------|

|           |            |

| В | Lite | ratur : | zu Alias- und Pointer-Analysen      | 212 |

|---|------|---------|-------------------------------------|-----|

|   |      | A.3.2   | Bedienung                           | 211 |

|   |      | A.3.1   | Voraussetzungen und Einschränkungen | 211 |

|   | A.3  | IR-C-I  | Konverter                           | 211 |

|   |      | A.2.5   | Compilierung und Installation       | 211 |

|   |      |         |                                     |     |

# Abbildungsverzeichnis

| Abhängigkeiten zwischen Programmen, Analysen, Optimierungen und Zielarchitektur | 13                                      |

|---------------------------------------------------------------------------------|-----------------------------------------|

| Prozessorkern der ADSP-21xx-Familie [2]                                         | 17                                      |

| Prozessorarchitektur des TI C60 [20]                                            | 18                                      |

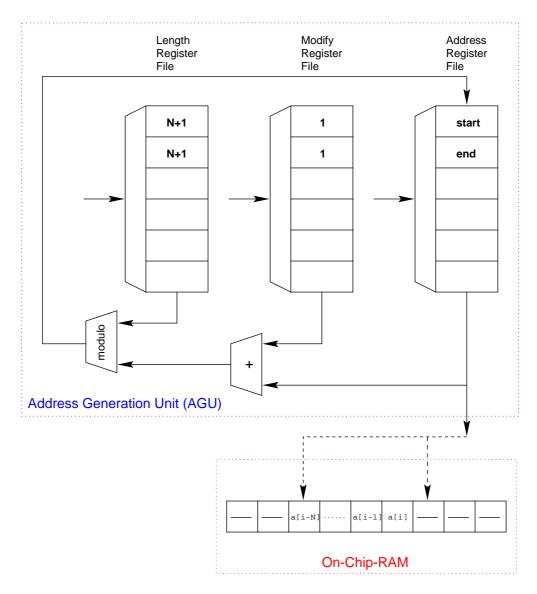

| AGU mit Address- und Modify-Registern                                           | 19                                      |

| Prinzip der seriellen Berechnung eines FIR-Filters mit Ringpuffer [21]          | 20                                      |

| AGU mit Address-, Modify- und Length-Register                                   | 21                                      |

| On-Chip-RAM beim TI TMS320C2x (nach [19])                                       | 22                                      |

| Exakte Lösung und Annäherungen durch Fixpunkte                                  | 38                                      |

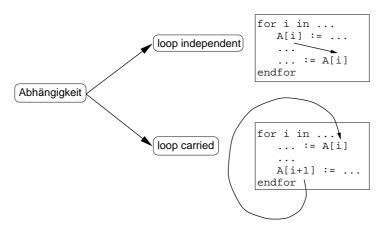

| Typen von Datenabhängigkeiten bei Array-Referenzen in Schleifen                 | 53                                      |

| Hasse-Diagramm des Verbandes mit der zugehörigen partiellen Ordnung             | 60                                      |

| Einzelner Knoten eines LCFG mit zugehörigen Komponenten                         | 62                                      |

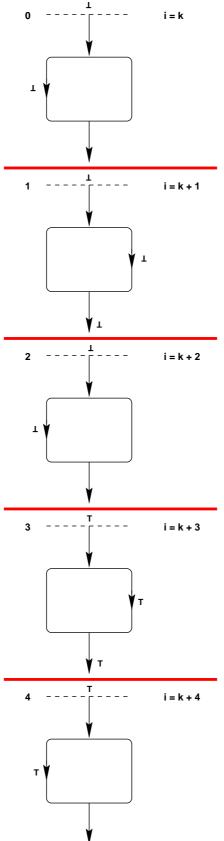

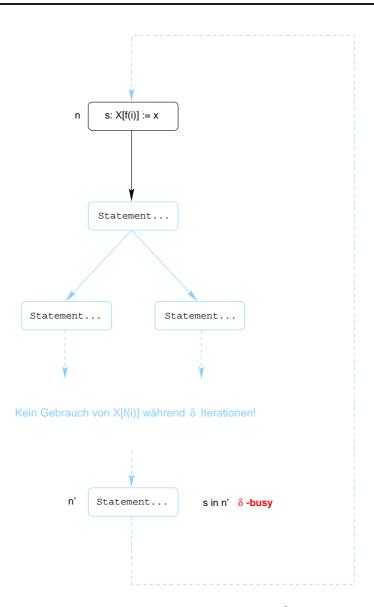

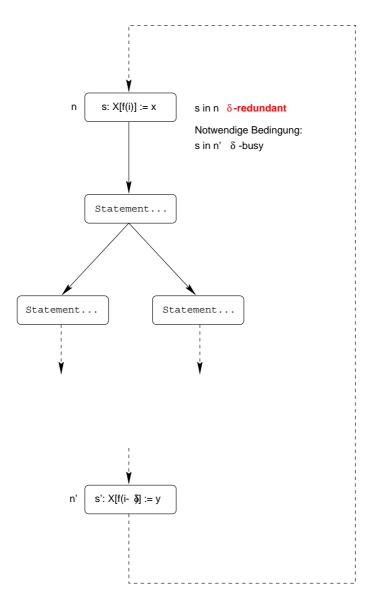

| Store s in Knoten n' $\delta$ -busy                                             | 121                                     |

| $\delta$ -redundantes Store s                                                   | 122                                     |

| Register-Pipeline mit Hardware-Unterstützung                                    | 160                                     |

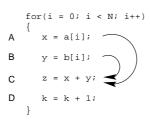

| Anwendung des Software-Pipelinings                                              | 168                                     |

| Schleife mit speicher- und wertebasierten Abhängigkeiten                        | 169                                     |

|                                                                                 | Prozessorkern der ADSP-21xx-Familie [2] |

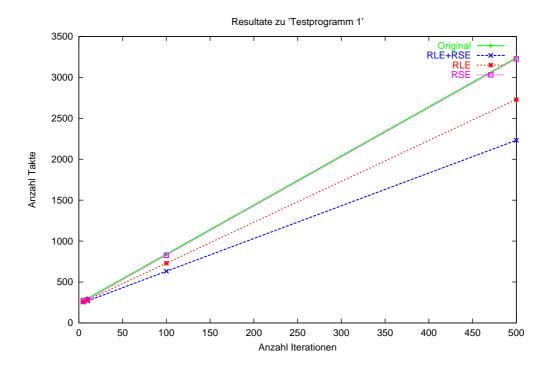

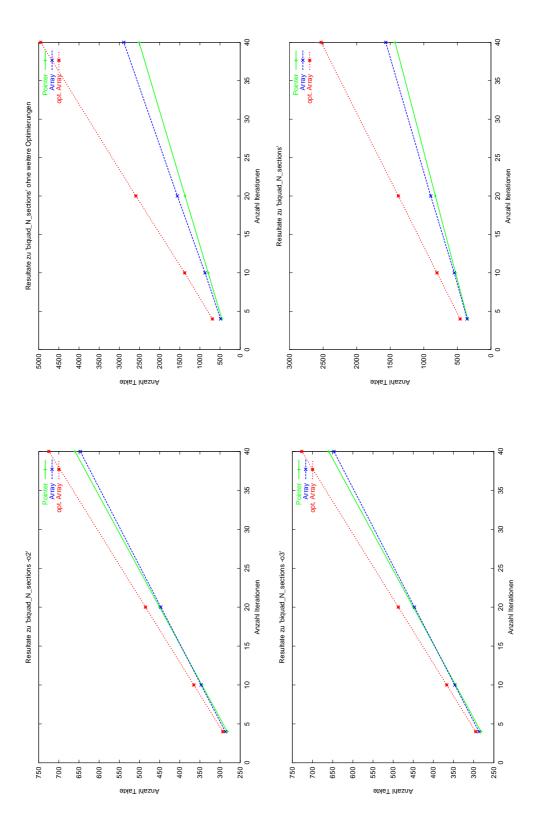

| 8.1 | Ausführungszeiten der Schleife mit einfachen, gemischten Referenzen                                                           |

|-----|-------------------------------------------------------------------------------------------------------------------------------|

| 8.2 | Ausführungszeiten der Schleife mit komplexeren, gemischten Referenzen                                                         |

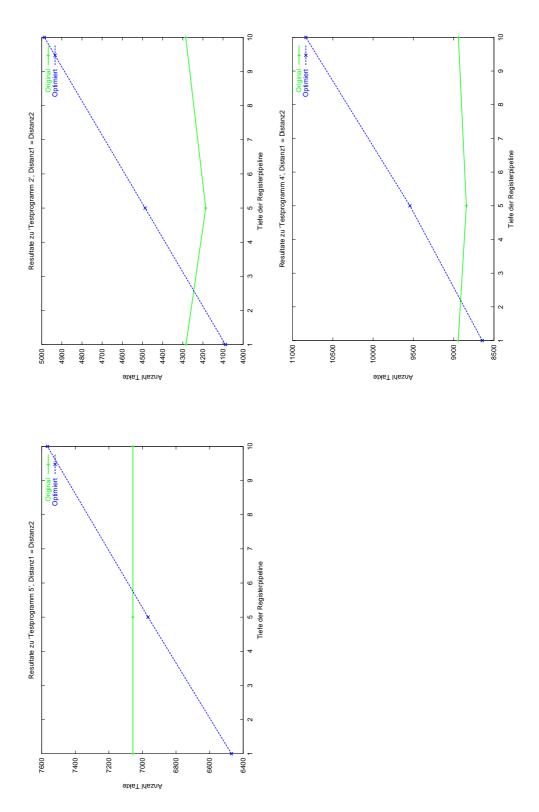

| 8.3 | Ausführungszeiten bei verschiedenen Iterationsdistanzen der Abhängigkeiten                                                    |

| 8.4 | Ausführungszeiten bei sehr großen Iterationsdistanzen der Abhängigkeiten                                                      |

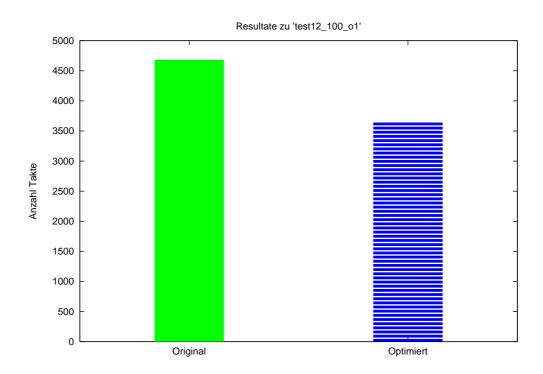

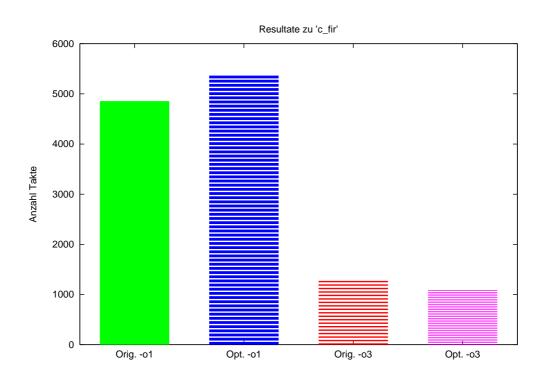

| 8.5 | Ausführungszeiten bei verschiedenen Optimierungsstufen 190                                                                    |

| 8.6 | Ausführungszeiten bei verschiedenen Optimierungsstufen 192                                                                    |

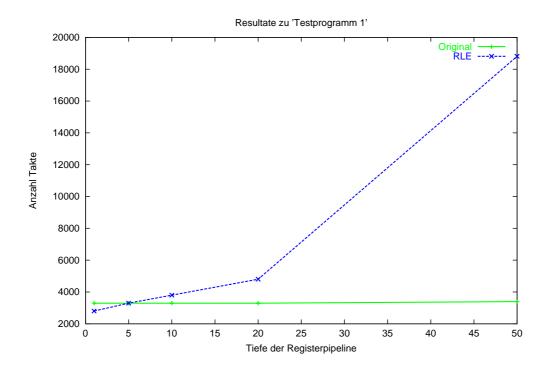

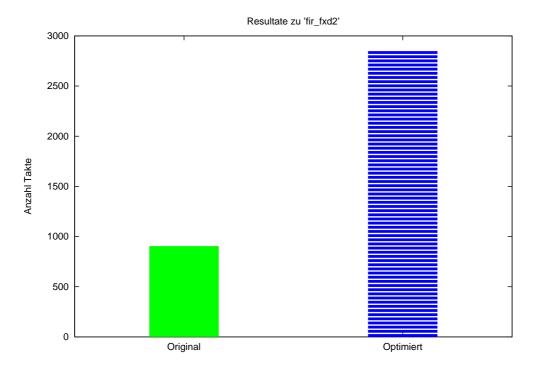

| 8.7 | Geschwindigkeitsverlust durch Optimierung                                                                                     |

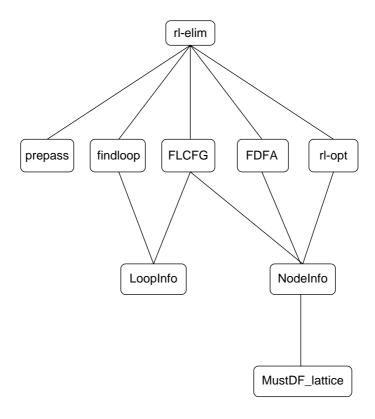

| A.1 | Wesentliche Verbindungen einzelner Programm-Module der Red-<br>undant Load Elimination                                        |

| A.2 | Zeitliche Abfolge der Bearbeitung während der <i>Redundant Load</i> Elimination und Zugehörigkeit zu den Programm-Modulen 208 |

## Kapitel 1

## Einleitung

Beim Einsatz von digitalen Signalprozessoren (DSP) in der Signalverarbeitung werden hohe Leistungsanforderungen gestellt. Zum einen muß eine große Geschwindigkeit in der Programmausführung erreicht werden, um den Durchsatzanforderungen zu genügen. Zum anderen gibt es strenge Grenzen des Speicherplatz- und Stromverbrauchs. Die Limitierung des Speicherplatzes ergibt sich aus den hohen Kosten für das Programm-ROM eines DSP, und aus den meist knappen Ressourcen des RAMs für den Datenspeicher. Der Stromverbrauch spielt vorwiegend in batteriebetriebenen, portablen Systemen, die einen DSP beinhalten, eine Rolle.

Ein möglicher Weg, den Anforderungen an DSP-Applikationen zu begegnen, liegt in der Optimierung von DSP-Programmen durch einen Compiler. Mit dem Ziel der Beschleunigung der Ausführung kann dieser versuchen, einen ähnlich guten Code zu generieren wie ihn ein erfahrener Assembler-Programmierer schreiben könnte. Das gewünschte Ziel wird jedoch vom Compiler nicht immer erreicht, es kann auch zu einer Verlangsamung kommen. Wenn eine Steigerung der Ausführungsgeschwindigkeit durch Programmoptimierungen erzielt wird, steht diese häufig in engem Zusammenhang mit dem Speicherplatzbedarf des Programms und dem Strombedarf des Prozessors. Viele Optimierungen beschleunigen nicht nur die Ausführung, sondern verkleinern gleichzeitig den Code-Umfang. Mit der Beschleunigung der Software können u.U. die Anforderungen an die Hardware zurückgenommen werden, z.B. durch Verminderung des Systemtakts oder durch den Einsatz weniger leistungsfähiger Prozessoren. Damit können der Stromverbrauch gesenkt oder Kosten gespart werden.

In der Vergangenheit sind viele Optimierungstechniken erarbeitet und vorgestellt worden ([1],[15],[3]). Diese wirken in sehr unterschiedlicher Weise und zielen in verschiedene Richtungen. Sie vermindern beispielsweise die Anzahl der Operationen zur Durchführung von Berechnungen, reorganisieren die Anordnung von Instruktionen zur Erzielung eines günstigeren Gesamtverhaltens, oder nutzen Informationen über die Zielarchitektur zur Anpassung des Ressourcenbedarfs von Programmen an das Ressourcenangebot des Prozessors. Unter

den vielen Möglichkeiten zu Programmoptimierungen gibt es die Klasse der Speicherzugriffsoptimierungen, die ihr Bemühen darauf richten, Speicherzugriffe effizienter zu gestalten. Geschehen kann das durch eine Verringerung der Anzahl von Speicherzugriffen oder durch eine bessere Ausnutzung einer evtl. vorhandenen Speicherhierarchie. Da bei vielen DSP der Speicher einen bottleneck bildet, kann der Ersatz von Speicherzugriffen durch Registerzugriffe zu erheblichen Performance-Steigerungen beitragen. Neben der Beschleunigung kann es zu Einsparungen beim Stromverbrauch kommen, denn Zugriffe auf externen Speicher über ein Bus-System verbrauchen viel Strom.

## 1.1 Ziele der Diplomarbeit

Im Rahmen der Recherche zu dieser Diplomarbeit wurden die Bereiche der Abhängigkeitsanalysen und Speicherzugriffsoptimierungen untersucht. Die beiden Bereiche können nicht unabhängig voneinander betrachtet werden, da Optimierungen spezielle Informationen benötigen, die von geeigneten Analysen bereitgestellt werden. Daher ist eines der Recherche-Ziele dieser Diplomarbeit herauszufinden, welche für DSP geeigneten Speicherzugriffsoptimierungen existieren, und durch welche Analysen sie ermöglicht werden. Dazu wird ein Schwerpunkt auf die Analyse und Optimierung von Array-Zugriffen in Schleifen gelegt. Schleifen bieten einen guten Ansatzpunkt für Optimierungsverfahren, da der größte Zeitanteil der Programmausführung in Schleifen verbraucht wird. Schon kleine Gewinne in einer Iteration summieren sich über den ganzen Iterationsbereich zu beträchtlichen Verbesserungen auf. In Schleifen wird bei typischen DSP-Anwendungen häufig auf Array-Elemente zugegriffen, die sich bei einfachen, konventionellen Verfahren der Analyse und Optimierung entziehen, so daß an dieser Stelle noch Potential für weitere Verbesserungen besteht.

Beispiel 1.1.1 Anwendung von Array-Redundanzeliminationen

```

Original:

Optimiert:

for(i = 0; i < 1000; i++)

t = a[0];

for(i = 0; i < 1000; i++)

if (cond)

{

if (cond)

x = a[i];

x = t;

}

}

a[i+1] = y;

}

t = y;

a[i+1] = t;

}

```

Beispiel 1.1.1 zeigt eine Programmschleife mit Zugriffen auf Array-Elemente und eine optimierte Schleifenvariante. In der Original-Version werden in jeder

12 Einleitung

Iteration zwei Zugriffe auf das Array a durchgeführt, davon kann der lesende Zugriffa[i] entfallen. Wenn eine Hilfsvariable t eingeführt wird, die dafür sorgt, daß der geschriebene Wert von a[i+1] in die nächste Iteration transportiert wird, kann der Zugriff auf das Array durch einen Zugriff auf die Hilfsvariable ersetzt werden. Wenn es zusätzlich noch gelingt, die Variable t in einem Register unterzubringen, kann beim gegebenen Beispiel die Anzahl der Speicherzugriffe für das Array a von 2000 auf 1001 reduziert werden. Positve Auswirkungen der Optimierung bestehen in der Beschleunigung der Programmausführung und der Entlastung des Speicherbusses. Als ungünstig könnten sich der Bedarf eines weiteren Registers im Schleifenkörper und der leicht angestiegene Code-Umfang erweisen.

Zur Durchführung der beschriebenen Optimierung ist die Information notwendig, daß a[i+1] und a[i] in aufeinanderfolgenden Iterationen das gleiche Daten-Element bezeichnen und a[i+1], ohne zuvor überschrieben worden zu sein, auch beim Gebrauch von a[i] eintrifft. Mit Datenflußanalysen, die für skalare Variable entwickelt wurden, kann diese Information nicht erlangt werden, da sie nicht mit der Situation umgehen können, daß ein Datenobjekt zwei verschiedene Bezeichnungen zur Laufzeit haben kann (hier a[i] und a[i+1]).

Nicht nur die Elimination redundanter Speicherzugriffe trägt zur Steigerung der Effizienz von Speicherzugriffen bei. Auch die Nutzung von Hardware-Ressourcen zur Unterstützung von Speicherzugriffen können diese effizienter werden lassen. Wenn das in DSP vorhandene On-Chip-RAM und die AGU verstärkt genutzt werden, kann, ohne die Anzahl der Speicherzugriffe zu verringern, eine Performance-Steigerung erreicht werden.

Es muß geklärt werden, welche Analysen zur Durchführung geeigneter Optimierungen erforderlich sind, und wie sie realisiert werden. Die Verbindungen zwischen Analysen und Optimierungen müssen aber auch dahingehend untersucht werden, wie die Informationsqualität der Analysen die Optimierungsgüte beeinflußt. Darüberhinaus soll geklärt werden, welche weiteren Optimierungen von den Analysen profitieren können und welche Vor- oder Nachteile sie bei DSP-Architekturen haben. Die Wechselwirkungen von verschiedenen Optimierungen untereinander und mit der Zielarchitektur sind wichtig für die Auswahl und den Einsatz der Optimierungen.

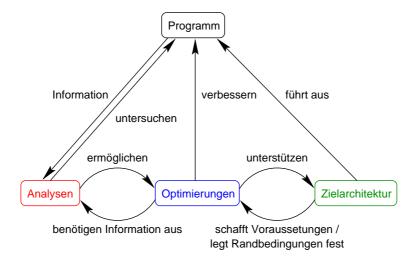

Abbildung 1.1 verdeutlich die Abhängigkeitsverhältnissse zwischen Programmen, deren Analysen und Optimierungen sowie der Zielarchitektur. Einem gegebenen Programm entnehmen die Analysen Informationen, z.B. über Verwendungen von Variablen oder gemeinsame Teilausdrücke. Zur Informationsentnahme müssen die Analysen aktiv das Programm untersuchen, und gewinnen daraus zusammengefaßte Aussagen über bestimmte Eigenschaften. Die Optimierungen benötigen die Informationen aus geeigneten Analysen. Häufig geht die Güte der Analyse in die Güte einer Optimierung ein oder schafft gar erst die Voraussetzungen zu deren Anwendung. Zur anderen Seite unterstützen Optimierungen bestimmte Eigenschaften der Zielarchitektur bei der Verbesserung des Programms, damit eine möglichst hohe Leistung erzielt werden kann. Die

Abbildung 1.1: Abhängigkeiten zwischen Programmen, Analysen, Optimierungen und Zielarchitektur

Optimierungen müssen auf durch die Zielarchitektur geschaffene Voraussetzungen Rücksicht nehmen, denn nicht jede Optimierung führt automatisch und unabhängig von der Prozessorarchitektur zu den gewünschten Verbesserungen der Systemeigenschaften. Letztendlich kann das Programm vom Prozessor ausgeführt werden.

Konkretes Ziel dieser Diplomarbeit ist die Beantwortung folgender Fragen:

- Welche Datenabhängigkeitsanalysen sind bislang entwickelt worden und was leisten sie?

- Welche Anforderungen werden an Datenflußanalysen für Array-Elemente gestellt und wie können sie erfüllt werden?

- Welche Array-Datenflußanalysen stehen zur Verfügung und wodurch unterscheiden sie sich?

- Welche Datenabhängigkeitsanalysen sind zur Unterstützung von Speicherzugriffsoptimierungen für DSP geeignet?

- Welche Speicherzugriffsoptimierungen sind geeignet für digitale Signalprozessoren?

- Können die Besonderheiten der Prozessorarchitektur von DSP zur Unterstützung von Speicherzugriffsoptimierungen genutzt werden?

- Welche Vor- und Nachteile ergeben sich aus der Anwendung einer Speicherzugriffsoptimierung?

- Wie hängt die Ausprägung des Registersatzes eines DSP mit dem Erfolg bzw. der Anwendbarkeit einer Optimierung zusammen?

14 Einleitung

• Welche weiteren Optimierungen können von Array-Datenflußanalysen profitieren?

## 1.2 Überblick

Kapitel 2 dieser Diplomarbeit führt in die Grundlagen von DSP-Architekturen ein. Besondere Berücksichtigung erfahren deren Registersätze und Adressierungseinheiten sowie das On-Chip-RAM als Komponenten, die von Bedeutung für Speicherzugriffsoptimierungen sind. Kapitel 3 stellt die Grundlagen von Datenflußanalysen und Optimierungen für skalare Variable dar, auf die in den darauf folgenden Kapiteln zurückgegriffen wird. In Kapitel 4 werden verschiedene Verfahren für die Datenflußanalyse von Array-Elementen vorgestellt. Die Analysen verfolgen z.T. verschiedene Ansätze und haben unterschiedliche Komplexität. Die Qualität der Analyse-Ergebnisse variiert für ein eingeschränktes Datenflußproblem zwischen Näherungslösung und exakter Lösung. In Kapitel 5 werden die Grundversionen von Load/Store-Redundanzeliminationen gezeigt, die die Ergebnisse von Array-Datenflußanalysen nutzbringend verwerten. In Kapitel 6 werden Varianten der vorangegangen Optimierungen diskutiert, die den möglichen Einsatzbereich erweitern oder die Optimierungsqualität verbessern. Zudem wird eine Version der Optimierung Register-Pipelining erläutert, die mit der Hardware-Unterstützung der Adressierungseinheit und des On-Chip-RAM eines DSP weitere Effizienzsteigerungen bewirken kann. Weitere Optimierungen, die für die Verbesserung von DSP-Programmen nützlich sein können, kommen in Kapitel 7 hinzu. Diese Optimierungen werden entweder durch die vorgestellten Array-Datenflußanalysen gegenüber bekannten Standardversionen verbessert, sind aber selbst keine Speicherzugriffsoptimierungen, oder verwenden eigene, spezielle Analysen. In Kapitel 8 werden Versuche dokumentiert, die mit im Rahmen der Diplomarbeit implementierten Array-Datenflußanalysen und Load/Store-Redunanzoptimierungen durchgeführt wurden. Im letzten Kapitel werden schließlich die Ergebnisse dieser Diplomarbeit zusammengefaßt und es wird auf Ausblick auf weitere Aspekte des Themengebietes gegeben, die in dieser Diplomarbeit nicht behandelt werden. Im Anhang werden die Implementationen der Optimierungen dokumentiert, mit denen die Versuche aus Kapitel 8 durchgeführt wurden. Eine Literaturliste, die dazu genutzt werden kann, einen Einstieg in das Gebiet der Pointer-Analyse zu finden, ist zusätzlich im Anhang untergebracht.

## Kapitel 2

## **DSP-Architekturen**

Digitale Signalprozessoren (DSP) sind Prozessoren, die in ihren Architekturmerkmalen ihrem Haupteinsatzgebiet – der digitalen Signalverarbeitung – entgegenkommen. In vielen Bereichen der digitalen Signalverarbeitung kommt es darauf an, daß eine große Menge von Daten erfaßt und nahezu zeitgleich verarbeitet wird. Der tolerierbare Zeitverzug zwischen der Datenerfassung und der Ausgabe der verarbeiteten Daten ist oft sehr klein, so daß an DSP hohe Anforderungen bezüglich des Durchsatzes gestellt werden. Um diesen Anforderungen zu genügen, muß ein besonderer Augenmerk auf die Konzeption der Verarbeitungseinheiten wie auch des Speichersystems digitaler Signalprozessoren gelegt werden.

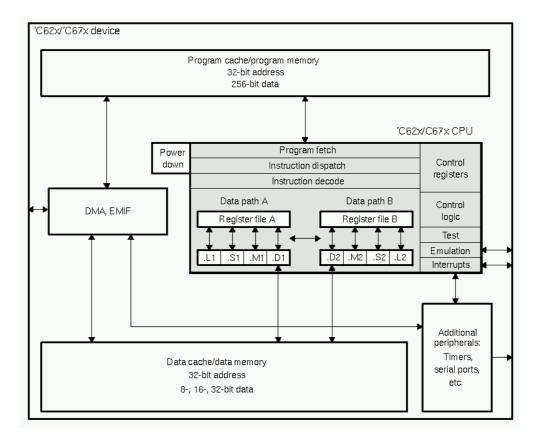

Zur Steigerung der Leistung der funktionalen Einheiten wird bei DSP oft auf Parallelverarbeitung, genauer auf instruktionsparallele Verarbeitung, zurückgegriffen. Nach [17] ist ein Instruction-Level Parallel (ILP) Prozessor ein paralleler Prozessor, dessen kleinste Berechnungseinheit, für die Scheduling- und Synchronisationsenscheidungen zu treffen sind, eine einzelne Operation ist. Dabei wird nicht unterschieden, ob entsprechende Entscheidungen zur Laufzeit eines Programms gefällt werden, oder schon während der Compilierung erfolgen. Unter diese Definition fallen VLIW-Prozessoren, da für sie Scheduling-Entscheidungen vom Compiler getroffen werden, ebenso wie superskalare Prozessoren, die z.B. durch dynamisches Instruction Scheduling erst zur Ausführung diese Entscheidungen treffen. Viele DSP besitzen VLIW-Architekturmerkmale (z.B. TI C60, siehe Abb. 2.2), so daß auch sie der Klasse der ILP-Prozessoren zuzuordnen sind.

In dieser Diplomarbeit stehen Belange der Datenverarbeitung – im Sinne von Berechnungen – durch DSP eher im Hintergrund, wichtiger in diesem Zusammenhang sind Besonderheiten digitaler Signalprozessoren im Bezug auf ihr Speichersystem. Dieses umfaßt Register, On-Chip- und Off-Chip-RAM sowie die sie verbindenden Bussysteme und zur Adressierung genutzte Adreßgenerierungseinheiten (Address Generation Unit, AGU). Die folgenden Abschnitte geben einen kurzen Überblick über die wichtigsten Unterschiede der Architek-

16 DSP-Architekturen

turmerkmale der Komponenten von Speichersystemen gängiger DSP gegenüber konventionellen General-purpose-Prozessoren.

## 2.1 Registersätze

Unter den DSP haben sich zwei verschiedene Klassen bzgl. ihrer Registersätze entwickelt. Zum einen sind heterogene Registersätze anzutreffen, bei denen die Register des Prozessors im Datenpfad verteilt und eng mit den funktionalen Einheiten verknüpft sind. Zum anderen gibt es DSP mit homogenen Registersätzen, die in Anlehnung an RISC-Prozessoren größere, allgemeine Registerbänke haben. Deren Register weisen i.a. keine zwingende Zuordnung zu funktionalen Einheiten – wie Addierern und Multiplizierern – auf und können frei verwendet werden.

## 2.1.1 Heterogene Registersätze

Registersätze, die mit funktionalen Einheiten eines DSP gekoppelt und evtl. sogar im Datenpfad verteilt sind, heißen heterogene Registersätze. Diese Art der Registersätze kommt i.a. den meist durchgeführten Operationen typischer DSP-Anwendungen entgegen. Eine Reihe von häufig benötigten Berechnungen werden effizient durch diese Prozessorarchitektur unterstützt. Für viele Anwendungen, z.B. Filter-Realisationen, werden fortlaufend mehr oder minder gleiche Berechnungen durchgeführt, die von einer allgemeineren Prozessorarchitektur nicht profitieren. So verfolgt die Anpassung der Architektur an die Anwendung nicht nur das Ziel der Effizienzsteigerung, sondern auch der Kostenminderung.

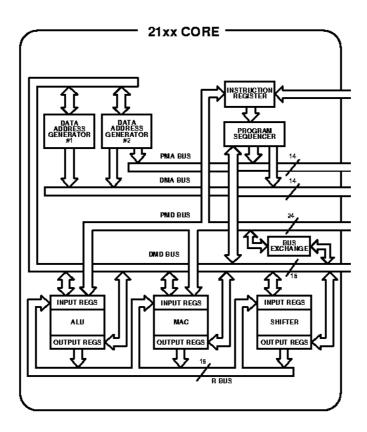

Abbildung 2.1 [2] zeigt den Prozessorkern der ADSP-21xx-Familie. Im unteren Bildteil befindet sich die arithmetische Einheit, die aus der ALU, einer MAC-Einheit und einem Shifter besteht. Jede der drei voneinander unabhängigen funktionalen Einheiten hat Eingabe- und Ausgabe-Register. In die Eingabe-Register werden Werte geschrieben, die als Operanden späterer arithmetischer Operationen dienen. Die Ausgabe-Register nehmen die von den Berchnungseinheiten gelieferten Resultate auf. Untereinander sind die Eingabe- und Ausgabe-Register mit einem Registerbus verbunden, um Werte aus den Ausgabe-Registern einer Einheit in Eingabe-Register der gleichen oder einer anderen Einheit zu transferieren. Zusätzlich sind die Eingabe- und Ausgabe-Register mit dem prozessor-internen Datenbus verbunden. Darüber können Werte geladen oder geschrieben werden, die von anderen internen oder externen Komponenten stammen oder dorthin gelangen sollen.

Werte, die in den Eingabe-Registern einer funktionalen Einheit gehalten werden, stehen den übrigen Einheiten nicht ohne weiteres zur Verfügung. Sie müssen erst durch Umkopieren in deren Eingabe-Register gebracht werden.

Abbildung 2.1: Prozessorkern der ADSP-21xx-Familie [2]

### 2.1.2 Homogene Registersätze

Mit immer komplexeren und immer vielfältigeren Aufgaben für DSP lassen sich verteilte Registersätze nicht mehr uneingeschränkt beibehalten. Zum einen ist die Spannweite möglicher Einsatzfelder von DSP sehr groß und die jeweils typischen Berechnungen variieren voneinander. Somit kann eine feste Auslegung der Architektur auf einen einzelnen Anwendungsfall unvorteilhaft sein. Zum anderen erschweren heterogene Registersätze Programmierern und/oder Compilern die Erzeugung von Code, der die vorhandenen Ressourcen optimal nutzt. Allgemein verwendbare Register, die nicht bestimmten funktionalen Einheiten zugeordnet sind, erleichtern den systematischen Umgang mit den Registern während der Code-Erzeugung. Dies hat zur Entwicklung einer Reihe von DSP mit homogenen Registersätzen geführt. Die meisten Register haben dabei keine spezifische Aufgaben- oder Ressourcen-Zuteilung, zudem ist häufig die Anzahl der verfügbaren Register höher als bei Architekturen mit heterogenen Registersätzen.

Abbildung 2.2 [20] zeigt ein Blockschaltbild der TI TMS320C62x-DSP-Familie. Grau unterlegt ist der Bereich des Prozessorkerns. In diesem befinden sich u.a. zwei Registerbänke A und B, die jeweils aus 16 32-Bit-Registern bestehen. Die beiden Registerbänke bilden zusammen mit acht funktionalen Einheiten zwei separate Datenpfade A und B. Jeweils vier der acht funktionalen Einheiten sind

18 DSP-Architekturen

in einem Datenpfad eingebettet. Alle Register stehen für allgemeine Aufgaben zur Verfügung, sie können Daten, Adreßzeiger oder Bedingungen enthalten.

Abbildung 2.2: Prozessorarchitektur des TI C60 [20]

Die funktionalen Einheiten eines Datenpfades arbeiten i.a. mit der Registerbank ihres Datenpfades. Sie entnehmen ihr die Operanden und speichern die Resultate dorthin zurück. Zwischen den beiden Datenpfaden gibt es Querverbindungen. Die funktionalen Einheiten einer Seite können jeweils auf einen 32-Bit-Operanden aus der Registerbank der anderen Seite zugreifen.

Die Verbindung der Registerbänke zum Speicher erfolgt über vier je 32 Bit breite Busse. Pro Registerbank existiert ein Pfad zum Laden von Werten aus dem Speicher und ein Pfad zum Speichern.

## 2.2 Address Generation Unit

Typische DSP-Programme arbeiten bevorzugt mit Array-Datenstrukturen auf die mit regelmäßigen Mustern zugegriffen wird. Zur Entlastung der arithmetischen Einheiten des Prozessorkerns von Adreßberechnungsaufgaben enthalten viele DSP Address Generation Units (AGU). Mit einer AGU kann parallel zur

Arbeit des Datenpfades die Adresse des nächsten Speicherzugriffs berechnet werden.

Die Verbindung einer AGU mit Post/Prä-Inkrement/Dekrement-Adressierungsarten erweist als besonders sinnvoll. Dadurch kann nach/vor einem Speicherzugriff die Adresse für den nächsten Zugriff um einen bestimmten Betrag erhöht/erniedrigt werden. Auf diese Weise lassen sich Array-Elemente effizient adressieren [4], denn der Speicherzugriff, die Adreßberechnung und u.U. Operationen der ALU finden gleichzeitig statt.

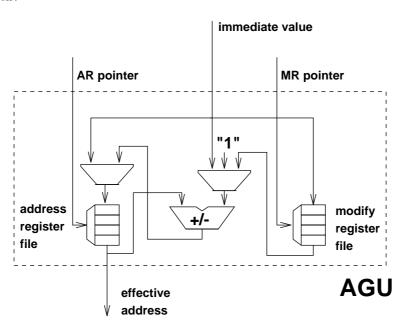

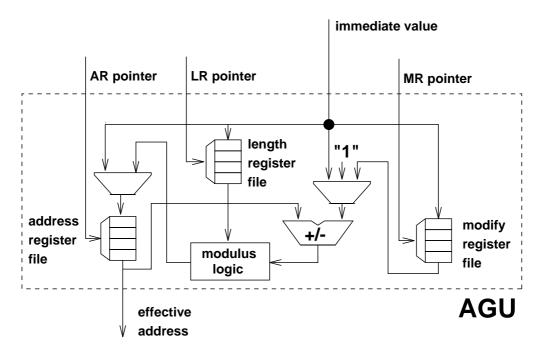

Abbildung<sup>1</sup> 2.3 zeigt den Aufbau einer einfachen AGU mit Adreß- und Modify-Registern. Anhand des Strukturbildes kann eine Post-Inkrement-Operation nachvollzogen werden. Aus dem Adreßregistersatz wird mit dem AR-Pointer ein einzelnes Register selektiert und dessen Inhalt wird als effektive Adresse auf den Adreßbus gelegt. Der Wert des selektierten Registers wird außerdem durch einen Addierer/Subtrahierer geführt, das Resultat wird zurück in das Adreßregister geschrieben. Der Summand bei dieser Operation kann eine konstante Eins, ein Direktoperand aus der Instruktion oder ein Wert aus der Modify-Registerbank sein. Damit sind unterschiedliche Schrittweiten der Zugriffe für verschieden große Array-Elemente zu realisieren. Für ILP-Prozessoren ergibt sich der Vorteil, daß Adreßarithmetik und Speicherzugriff zeitgleich mit den eigentlichen Berechnungen durchgeführt werden können. Die Zeiteinsparungen durch die exklusive Verwendung des Datenpfades für Programmdaten sind beträchtlich.

Abbildung 2.3: AGU mit Address- und Modify-Registern

Zum sequentiellen Adressieren eines short int-Arrays mit 16-Bit-Elementen

$<sup>^1\</sup>mathrm{Die}$  Abbildungen 2.3 und 2.5 wurden von Rainer Leupers freundlicherweise zur Verfügung gestellt. Nochmals einen herzlichen Dank !

20 DSP-Architekturen

ab der Adresse 100 wird ein Adreßregister mit dem Wert 100 geladen. Ein Modify-Register wird mit dem Wert 2 geladen, da die 16-Bit-Werte einen Abstand von 2 untereinander haben. Nach dem ersten Zugriff mit einer Post-Inkrement-Operation wird der Wert im Adreßregister durch 102 ersetzt. Nachfolgende Adressen ergeben sich zu 104, 106, .... Soll neben neben dem short int-Array auch noch ein long int-Array mit 32-Bit-Elementen ab der Adresse 200 adressiert werden, so wird in einem anderen Adreßregister die Startadresse 200 gespeichert. In ein Modify-Register wird der Wert 4 geschrieben. Die Adressen einer Reihe von Zugriffen mit Post-Inkrement sind 200, 204, 208, ....

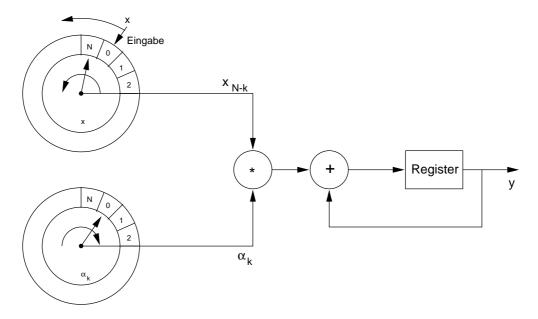

Bei der Realisation von FIR-Filtern [21] – einer häufigen und typischen DSP-Applikation – werden zwei Schieberegister benötigt. Diese werden üblicherweise mit Arrays implementiert, die als Ringpuffer organisiert sind. Dazu brauchen keine Inhalte verschoben und kopiert zu werden, sondern es reicht aus mit zwei Zeigern den Anfang und das Ende der Queue zu adressieren. Abbildung 2.4 zeigt die beiden Ringpuffer zusammen mit einem Multiplizierer-Akkumulator für einen FIR-Filter mit folgender Zeitfunktion:

$$y(t_N) = \sum_{k=0}^{N} \alpha_k x(t_{N-k})$$

(2.1)

Abbildung 2.4: Prinzip der seriellen Berechnung eines FIR-Filters mit Ringpuffer [21]

Zur hardware-seitigen Unterstützung der für die Implementierung von Ringpuffern benötigten zirkularen Adressierung besitzen viele DSP Adressierungseinheiten mit einer Modulo-Logik. Diese bewirkt, daß bei einer Post/Prä-Inkrement/Dekrement-Operation der in das Adreßregister zurückgeschriebene Wert zuvor einer Modulo-Operation unterzogen wird. Abbildung 2.5 zeigt die Struktur einer solchen AGU. In einer Length-Register-Bank werden Werte gehalten,

die der Modulo-Logik zugeführt werden. Die aus dem Addierer/Subtrahierer kommenden Werte werden diesem Modulo unterzogen.

Abbildung 2.5: AGU mit Address-, Modify- und Length-Register

## 2.3 Speicherorganisation und On-Chip-RAM

DSP werden häufig als Harvard-Architekturen realisiert, die getrennte Datenund Programmspeicher mit separaten Bussen vorsehen. Das ermöglicht den gleichzeitigen Transport von Instruktionen und Daten, was zu einer höheren Ausnutzung der Ressourcen und damit zur Steigerung der Effizienz beiträgt. Nach außen hin werden gelegentlich der Daten- und Programmbus zur Vereinfachung der äußeren Umgebung über einen externen Bus im Multiplex betrieben.

Viele DSP besitzen sowohl internen Speicher (On-Chip-RAM) als auch die Möglichkeit, über ein Bus-System externen Speicher zu adressieren. Der interne Speicher ist meist klein gegenüber dem gesamten Adreßraum, auf ihn kann ohne Verzögerungen zugegriffen werden. Der externe Speicher kann je nach Ausbau erheblich größer sein und ist abhängig von der Art des Speichers (SRAM,DRAM, ...) und der Leistungsfähigkeit des Bus-Systems langsamer. Interner und externer Speicher liegen meistens im gleichen Adreßraum, d.h. es müssen keine gesonderten Instruktionen zur Adressierung verwendet oder Segmentregister zuvor geladen werden.

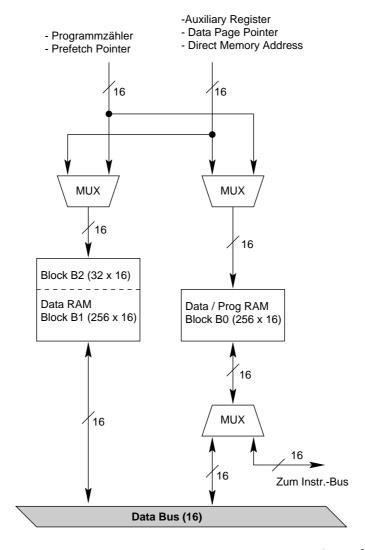

Abbildung 2.6 zeigt das On-Chip-RAM bei einem TI TMS320C2x. Es besteht aus drei Blöcken, wovon einer (B0) als Daten- oder Programmspeicher konfiguriert werden kann. Die beiden übrigen (B1 und B2) sind immer Datenspeicher.

22 DSP-Architekturen

Das On-Chip-RAM kann ohne Wait-States angesprochen werden. Ein bis zu 64k großes externes RAM kann über das Bus-System adressiert werden. Über Multiplexer wird der Speicher vom Programmzähler oder vom Data-Page-Pointer adressiert (andere Quellen von Adressen sind möglich). Zum Datentransport sind die Blöcke B1 und B2 direkt mit dem Datenbus und B0 über einen Multiplexer mit dem Daten- und Programmbus verbunden.

Abbildung 2.6: On-Chip-RAM beim TI TMS320C2x (nach [19])

Da die Größe des On-Chip-RAM mit 544 Speicherworten klein bemessen ist, sollten nur häufig frequentierte Daten dort abgelegt werden, um von der hohen Zugriffsgeschwindigkeit effizient Gebrauch zu machen. Verfahren zur Partitionierung von Daten auf On- und Off-Chip-RAM finden sich in [16] und [18].

Zum gleichzeitigen Zugriff auf zwei Operanden ermöglichen einige DSP (u.a. ADSP-21xx, TI C60) die *Dual Memory Execution*. Damit können zwei Speicherzugriffe parallel erfolgen, so daß z.B. zwei für eine Operation benötigte Operanden gleichzeitig aus dem Speicher in Register transferiert werden können.

## 2.4 Weitere Literatur

• Lapsley, P.

DSP processor fundamentals: architectures and features

IEEE Press, New York, 1997.

## Kapitel 3

## Datenabhängigkeit, Analysen, Optimierungen

Zur Durchführung von Programmoptimierungen sind einige Vorarbeiten notwendig, denn eine Optimierung muß wissen, an welchen Stellen sie Einsatz finden kann. Zudem darf sie nicht willkürlich das Programmverhalten ändern, denn eine Optimierung darf nicht die Korrektheit eines Programms riskieren. Die Ausführung der einzelnen Operationen unterliegt bestimmten Abhängigkeiten, seien es beispielsweise Abhängigkeiten von Verzweigungsbedingungen oder Abhängigkeiten von zuvor berechneten Werten, die für folgende Berechnungen benötigt werden. Auf diese Abhängigkeiten müssen Optimierungen Rücksicht nehmen. Die Ermittlung der relevanten Abhängigkeiten erfolgt durch Abhängigkeitsanalysen. Der Schwerpunkt liegt dabei auf *Datenabhängigkeiten*, die sich durch den wiederholten Zugriff verschiedener Instruktionen auf gemeinsame Daten ergeben.

## 3.1 Grundlegende Begriffe

Die Darstellung eines Programms durch seinen Quelltext oder durch eine Zwischendarstellung (IR, intermediate representation), die einer konventionellen Maschinensprache ähnlich ist, ist nicht für alle Analyseaufgaben eines Compilers geeignet. Wenn beispielsweise untersucht werden soll, ob ein bestimmtes Statement von einem anderen aus zu erreichen ist, so bietet sich eher eine Darstellung durch einen gerichteten Graphen an. Die Knoten des erzeugten Graphen repräsentieren einzelne Instruktionen und seine Kanten Kontrollflußübergänge zwischen Instruktionen.

**Definition 3.1.1** Ein Kontrollflußgraph (CFG<sup>1</sup>) ist ein Graph G = (N, E, s, e) mit der Knotenmenge N, der Kantenmenge  $E \subseteq N \times N$ , einem Startknoten

<sup>&</sup>lt;sup>1</sup>Control Flow Graph

s und einem Endknoten e mit  $s,e \in N$ . Wenn n ein direkter Kontrollflußvorgänger von m ist, so gilt  $(n,m) \in E$ . n ist Vorgänger von m, m ist ein Nachfolger von n. Der Startknoten s hat keinen Vorgänger, der Endknoten e keinen Nachfolger.

**Definition 3.1.2** Ein Pfad  $\pi$  in einem CFG(N, E, s, e) besteht aus einer Folge von Kanten.  $\pi$  beginnt an einem Knoten  $n_1$  und endet an einem Knoten  $n_k$ :  $\pi = (n_1, n_2), (n_2, n_3), \ldots, (n_{k-1}, n_k)$  mit  $(n_i, n_{i+1}) \in E, i < k$ . Ein Pfad, der bei einem Knoten  $n_i$  beginnt und bei  $n_j$  endet, wird durch  $n_i \rightsquigarrow n_j$  beschrieben.

Kontrollflußgraphen bilden die Grundlage vieler Programmanalysen, da sie auf einfache und intuitive Weise mögliche Ausführungsreihenfolgen von Instruktionen modellieren.

Innerhalb von Kontrollflußgraphen können "zusammengehörige" Abschnitte zu einem Basisblock zusammengefaßt werden. In einem Programm sind Basisblöcke Programmfragmente, die immer "am Stück" ausgeführt werden. Wird die erste Instruktion eines Basisblocks ausgeführt, so wird auch unweigerlich dessen letzte Instruktion ausgeführt. In einem Basisblock gibt es keine Verzweigungen oder Sprungziele. Daher besteht keine Möglichkeit, einen Basisblock "in der Mitte" durch eine Verzweigung zu verlassen, oder durch einen Sprung dorthin zu gelangen.

**Definition 3.1.3** Eine Basisblock ist eine Folge von Knoten  $(n_1, \ldots, n_k)$  eines  $CFG\ FG = (N, E, s, e)$ , so daß  $n_i$  der einzige Vorgänger von  $n_{i+1}$  ist, und  $n_{i+1}$  der einzige Nachfolger von  $n_i$  ist.

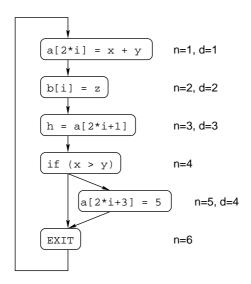

Beispiel 3.1.1 Schleifen mit mehreren Ein-/Ausgängen

Die meisten Kontrollflußgraphen enthalten Zyklen mit mehreren beteiligten Knoten. Alle an einem Zyklus beteiligten Knoten bilden eine Schleife (loop).

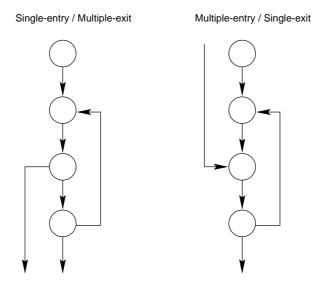

Wenn es einen Knoten gibt, über den alle Pfade von Startknoten s zu den Schleifenknoten führen müssen, d.h. dieser Knoten der einzige Knoten ist, der in die Schleife führt, dann besitzt die Schleife die Single-entry-Eigenschaft. Analog hat eine Schleife die Single-exit-Eigenschaft, wenn es einen Knoten gibt, über den alle Pfade aus der Schleife zum Endknoten e führen müssen. Schleifen, deren Pfade in die Schleife hinein oder aus der Schleife heraus über mehrere alternative Knoten verlaufen können, haben die Multiple-entry- bzw. Multiple-exit-Eigenschaft. Beispiel 3.1.1 zeigt verschiedene Schleifen mit den gerade genannten Eigenschaften.

Single-entry/Single-exit-Schleifen, die aus programmiersprachlichen Konstrukten wie for i= ... enstehen, also eine festgelegte Anzahl Iterationen<sup>2</sup> absolvieren, und auch nicht vorzeitig durch Sprünge beendet werden, heißen strukturierte Schleifen (Beispiel 3.1.2,a)).

### Beispiel 3.1.2 Verschiedene Schleifentypen

#### a) Strukturierte Schleife b) Enge Schleifenschachtelung for(i = 0; i < 100; i++)for(i = 0; i < 100; i++)₹ a = x;for(j = 0; j < 100; j++)if (a > y) { for (k = 0; k < 100; k++)b = c;} { a[i][j][k] = 5;else { x = y;b[k] = f(k);} } } } }

Strukturierte Schleifen Schleifen haben einen Schleifenkopf mit der Initialisierung und dem Test des Abbruchkriteriums, sowie einen Schleifenkörper, der aus der Sequenz von wiederholt ausgeführten Instruktionen besteht. Werden mehrere Schleifen ineinander geschachtelt, so liegt eine Schleifenschachtelung (loop nest) vor. Eine besondere Art eines loop nest ist dann gegeben, wenn mehrere strukturierte Schleifen direkt ineinander geschachtelt sind, d.h. alle Schleifen bis auf die innerste enthalten ausschließlich ein Statement, nämlich eine strukturierte Schleife. Eine solche Schleifenschachtelung wird enge Schleifenschachtelung (tight loop nest) (Beispiel 3.1.2,b) ) genannt.

<sup>&</sup>lt;sup>2</sup>Dazu gehört auch, daß die *Induktionsvariable i* im Schleifenkörper nicht redefiniert wird.

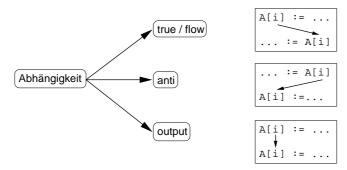

## 3.2 Abhängigkeitsrelationen

Die Abhängigkeiten der Instruktionen untereinander können durch Relationen beschrieben werden. Zum einen gibt es Abhängigkeiten zwischen Instruktionen aufgrund der Einschränkungen der Ausführungsreihenfolge durch den Kontrollfluß, zum anderen können Abhängigkeiten zwischen Instruktionen wegen gemeinsam benutzter Daten auftreten.

**Definition 3.2.1** Zwei Instruktionen  $S_1$  und  $S_2$  stehen genau dann zueinander in der Relation  $S_1 \triangleleft S_2$ , wenn die Instruktion  $S_1$  der Instruktion  $S_2$  in der Ausführungsreihenfolge vorangeht, also im CFG ein Pfad  $S_1 \rightsquigarrow S_2$  existiert.

Abhängigkeiten zwischen Instruktionen können deren Ausführungsreihenfolge einschränken. Je nach Ursache einer Abhängigkeit unterscheidet man zwischen Kontrollabhängigkeiten, die durch zwingend zu beachtende Kontrollstrukturen (IF... THEN... ELSE...) in Programmen entstehen, und Datenabhängigkeiten, bei denen eine Datum einer Instruktion in einer späteren (abhängigen) Instruktion erneut verwendet wird.

**Definition 3.2.2** Eine Kontrollabhängigkeit (control dependence) zwischen zwei Instruktionen erwächst aus dem Kontrollfluß eines Programms. Wenn eine Instruktion  $S_2$  abhängig von der Auswertung der Instruktion  $S_1$  ausgeführt wird, so ist  $S_2$  von  $S_1$  kontrollabhängig. Die formale Schreibweise dieser Kontrollabhängigkeit ist  $S_1\delta^cS_2$ .

#### Beispiel 3.2.1 Kontrollabhängigkeit

```

S_1: x = a;

S_2: if (x > 3)

S_3: b = b + 1;

```

In Beispiel 3.2.1 gibt es eine Kontrollabhängigkeit zwischen  $S_2$  und  $S_3$  ( $S_2\delta^cS_3$ ), da  $S_3$  nur dann ausgeführt wird, wenn die Bedingung in  $S_2$  wahr ist.

Bevor weitere Definitionen erfolgen können, muß eine feinere Differenzierung von Datenzugriffen getroffen werden. Ein lesender Zugriff auf eine Variable ist ein Gebrauch, während ein schreibender Zugriff eine Definition ist. Kommt es nicht auf die Art des Zugriffs an, d.h. es sind sowohl Gebräuche als auch Definitionen gemeint, kann von Referenzen gesprochen werden.

**Definition 3.2.3** Eine Datenabhängigkeit (data dependence) zwischen zwei Instruktionen ist eine mögliche Einschränkung der Ausführungsreihenfolge, die durch den Datenfluß zwischen diesen Instruktionen verursacht wird. Eine Instruktion  $S_2$  ist datenabhängig von  $S_1$  (formale Schreibweise  $S_1\delta^dS_2$ ), wenn eine in  $S_1$  referenzierte Variable in  $S_2$  erneut referenziert wird.

Die Definition der Datenabhängigkeit ist in dieser Form sehr allgemein, da nichts über die Art der Wiederverwendung des Datums ausgesagt wird. Eine genauere Unterscheidung der Datenabhängigkeit ergibt sich durch Differenzierung nach der Art Zugriffs (Lesen/Schreiben) in den beteiligten Instruktionen.

**Definition 3.2.4** Wenn  $S_1 \triangleleft S_2$  und  $S_1$  eine Variable definiert, die in  $S_2$  gebraucht und zwischen  $S_1$  und  $S_2$  nicht redefiniert wird, dann exisitiert zwischen  $S_1$  und  $S_2$  eine Datenflußabhängigkeit (flow dependence, true dependence).  $S_1$  und  $S_2$  stehen in der Relation  $S_1\delta^fS_2$  zueinander.

**Definition 3.2.5** Wenn  $S_1 \triangleleft S_2$  und  $S_1$  eine Variable gebraucht, die  $S_2$  definiert ohne eine Redefinition der betreffenden Variablen zwischen  $S_1$  und  $S_2$ , dann besteht zwischen  $S_1$  und  $S_2$  eine Antiabhängigkeit (antidependence)  $S_1\delta^aS_2$ .

**Definition 3.2.6** Wenn  $S_1 \triangleleft S_2$  und  $S_1$  und  $S_2$  die gleiche Variable definieren und zwischenzeitlich keine weitere Definition dieser Variablen erfolgt, besteht eine Ausgabeabhängigkeit (output dependence) zwischen  $S_1$  und  $S_2$ , bzw.  $S_1\delta^{\circ}S_2$ .

**Definition 3.2.7** Wenn  $S_1 \triangleleft S_2$  und  $S_1$  und  $S_2$  eine gemeinsame Variable lesen, die zwischenzeitlich nicht neu definiert wird, so existiert zwischen  $S_1$  und  $S_2$  eine Eingabeabhängigkeit (input dependence)  $S_1\delta^i S_2$ .

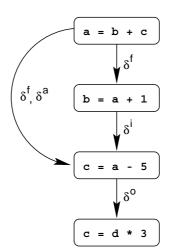

Beispiel 3.2.2 Abhängigkeiten und Abhängigkeitsgraph

#### Code fragment

## a = b + c; b = a + 1; c = a - 5; c = d \* 3;

#### $Abh\"{a}ngigkeitsgraph$

Von den vier Datenabhängigkeitsrelationen schränken die ersten drei die Ausführungsreihenfolge ein, nicht jedoch die vierte – die input dependence. Jedoch werden im Zusammenhang mit Optimierungen von Array-Zugriffen *Load-After-Load-*Situationen (siehe Kapitel 5.2) betrachtet, die dem Konzept der input dependence entsprechen.

Abhängigkeiten können durch gerichtete Graphen dargestellt werden, deren Knoten den Instruktionen entsprechen, und deren Kanten eine Abhängigkeit darstellen. Dabei wird eine Kante mit der Art der Abhängigkeit markiert. Für eine Abhängigkeit  $S_1\delta S_2$  wird die Kante von  $S_1$  nach  $S_2$  gerichtet. Beispiel 3.2.2 zeigt die Datenabhängigkeiten zu einem Code-Fragment in einem Abhängigkeitsgraphen.

## 3.3 Datenabhängigkeitsanalysen

Der Schwerpunkt dieser Arbeit liegt bei der Untersuchung und Behandlung von Datenabhängigkeiten. Daher sollen zunächst die grundlegenden Techniken der Datenflußanalyse, die u.a. in [3], [15] und [11] nachzulesen sind, erläutert werden.

Beispiel 3.3.1 zeigt ein kleines Programmfragment, welches daraufhin überprüft werden soll, ob es gemeinsame Teilausdrücke enthält, die entfernt werden können (siehe Bsp. 3.4.1 zu näheren Detail dieser Optimierung). Ein Kandidat ist der Ausdruck x+y, der zu Beginn und in der Schleife vorkommt. Eine Analyse erfolgt in einer graphischen Darstellung der Schleife, dem Kontrollflußgraphen. In einem ersten Analysedurchlauf werden der Reihe nach alle Knoten besucht. Für jeden Knoten wird als dessen Eigenschaft notiert, welche Ausdrücke nach seiner Ausführung verfügbar sind. Ein Ausdruck ist verfügbar, wenn er einmal ausgewertet wurde und seine Operanden im nachhinein nicht verändert werden. Nach Bearbeitung der Instruktion i<N ergibt sich ein Konflikt. Entgegen der Feststellung beim ersten Betrachten des Knotens b = x+y erreichen diesen Knoten von dem erst später betrachteten Knoten i<N andere Ausdrücke als zuvor. Die Lösung dieses Konfliktes liegt in der Bildung der Schnittmenge der Ausdrücke und einem weiteren Durchlauf. Damit wird sichergestellt, daß nur mit Ausdrücken gearbeitet wird, die den Knoten b = x+y auf allen Pfaden erreichen - in diesem Fall 1. Beim zweiten Durchlauf müssen die Ergebnisse des vorherigen Durchlaufs durch diese Veränderung revidiert werden. Am Ende des Durchlaufs wird für b = x+y wieder die Schnittmenge der eintreffenden Ausdrücke gebildet, es ergibt sich wie zuvor die 1. Weitere Durchläufe können das Ergebnis nicht mehr verändern, die Lösung hat sich stabilisiert. Damit kann die Analyse beendet werden. Für die Optimierung muß das Ergebnis interpretiert werden. Die Frage war, ob x+y in b=x+y durch den Ausdruck aus a=x+y ersetzt werden kann. Da der Ausdruck x+y die Instruktion b=x+y aber nicht zwingend erreicht - dies schafft nur der Ausdruck 1 - kann die Optimierung nicht durchgeführt werden.

Beispiel 3.3.1 Analyse eines Programmfragments

### Programmfragment mit Schleife

```

a = x + y;

c = 1;

for(i = 0; i < N; i++)

{

b = x + y;

x = x + 1;

}

1. Durchlauf

2. Durchlauf

a = x + y

х+у

х+у

c = 1

c = 1

x+y,1

x+y,1

i = 0

i = 0

Konflikt!

Schnittmenge

1

b = x + y

b = x + y

x+y, 1, 0

x+y,1

x = x + 1

x = x + 1

1,i<N

1.0

1

i = i + 1

i = i + 1

1

1

i < N

i < N

```

Die folgenden Abschnitte führen in die grundlegenden Techniken Datenabhängigkeitsanalyse ein. Nach der Einführung geeigneter Abhängigkeitsbegriffe im vorherigen Abschnitt wird gezeigt, wie darauf basierend Schritt für Schritt ein formales Modell eines zu analysierenden Programms erstellt werden kann. Die Eigenschaften – im Beispiel die Eigenschaft, daß ein Ausdruck einen Knoten erreicht – können durch Verbände realisiert werden. Das Erzeugen und Vernichten von Eigenschaften – im Beispiel, ob ein Ausdruck nach einem Knoten verfügbar ist oder ob ein Ausdruck einen Knoten "passieren" kann – wird durch Funktionen, die auf den Verbänden operieren, nachgebildet. Insgesamt bildet diese Modell die geeignete Voraussetzung zum Ansatz eines Verfahrens, daß die gewünschten Abhängigkeiten berechnen kann. Dazu wird wie im Beispiel iterativ vorgegangen bis sich die Knoteninformationen nicht weiter verändern. Mit der so gewonnen Information können nachfolgende Optimierungen ihre Arbeit aufnehmen.

Das Ziel der Datenflußanalyse ist es, bestimmte Eigenschaften bzgl. exisitierender Datenabhängigkeiten für alle Stellen eines gegebenen Programms zu berechnen. Diese Eigenschaften werden durch Werte einer Domäne D beschrieben.

Während und nach der Analyse werden alle Knoten n eines CFG mit Werten aus D versehen, welche die Gültigkeiten der betrachteten Eigenschaften vor und nach Ausführung der mit dem Knoten n verbundenen Instruktion<sup>3</sup> beschreiben. Die Auswirkungen einer Instruktion werden durch eine Transferfunktion  $f:D\to D$  modelliert, d.h. eine mögliche Veränderung einer vor Eintritt in n geltenden Eigenschaft wird überführt in den Zustand nach Verlassen von n. Die Transferfunktion wird immer dann angewendet, wenn der Kontrollfluß den Knoten n passiert. Dementsprechend bildet der CFG eines Programms, dessen Knoten mit Transferfunktionen versehen sind, ein spezielles Gleichungssystem, das Datenflußgleichungssystem.

#### 3.3.1 Datenflußverbände

Die Domäne D, durch die die zu analysierenden Eigenschaften abstrahiert werden, wird i.a. durch einen  $Verband\ L$  realisiert. Ein Verband bietet neben einer Menge von Werten, die den Eigenschaften, wie z.B. Gültigkeit eines zuvor definierten Ausdrucks, entsprechen, Operatoren für diese Werte. Dadurch können mehrere zusammenkommende Eigenschaften zu einer neuen kombiniert werden.

Im Eingangsbeispiel 3.3.1 besteht die Domäne D aus Aussagen über Ausdrücken, die in dem Programm vorkommen. Die Aussage, daß ein Ausdruck einen Knoten erreicht, kann wahr oder falsch sein. Die Schnittmengenbildung bei den zusammenlaufenden Kontrollflußpfaden ist ein Operator auf der Aussagenmenge. In praktischen Realisierungen werden statt der Mengenoperationen aussagenlogische Operatoren bevorzugt.

**Definition 3.3.1** Ein Verband L besteht aus einer Menge von Elementen, der Trägermenge, und zwei Operatoren  $\sqcap$  (meet) und  $\sqcup$  (join) mit folgenden Eigenschaften:

```

1. Abgeschlossenheit: \forall x, y \in L : \exists z, w \in L : x \sqcap y = z \land x \sqcup y = w

```

2. Kommutativität:

$$\forall x, y \in L : x \sqcap y = y \sqcap x \quad \land \quad x \sqcup y = y \sqcup x$$

3. Assoziativität:

$$\forall x,y,z \in L: (x\sqcap y) \sqcap z = x \sqcap (y\sqcap z) \quad \land \quad (x\sqcup y) \sqcup z = x \sqcup (y\sqcup z)$$

- 4. Supremum, Infimum:

- $\exists \bot \in L : \forall x \in L : x \sqcap \bot = \bot$

- $\exists \top \in L : \forall x \in L : x \sqcup \top = \top$

$Das\ Element \perp hei\beta t\ bottom, \ \top\ hei\beta t\ top.$

<sup>&</sup>lt;sup>3</sup>Anstelle einer einzelnen Instruktion kann auch eine zu einem Basisblock zusammengefaßte Sequenz von Instruktionen durch einen Knoten repräsentiert werden.

**Definition 3.3.2** Ein Verband L heißt distributiver Verband, falls zusätzlich gilt:

```

\forall x, y, z \in L : (x \sqcap y) \sqcup z = (x \sqcup z) \sqcap (y \sqcup z) \quad \land \quad (x \sqcup y) \sqcap z = (x \sqcap z) \sqcup (y \sqcap z)

```

**Definition 3.3.3** Die auf einem Verband L induzierte partielle Ordnung  $(L, \sqsubseteq)$  ist durch  $\forall x, y \in L : x \sqsubseteq y \iff x \sqcap y = x$  definiert. Die gleiche Definition ist auch mit dem  $\sqcup$ -Operator möglich.  $\sqsubseteq$ ,  $\sqsupset$  und  $\rightrightarrows$  sind analog definiert.

```

Definition 3.3.4 Die Höhe eines Verbandes L ist definiert als: height(L) = max\{n | \exists x_1, x_2, \dots, x_n : \bot = x_1 \sqsubseteq x_2 \sqsubseteq \dots \sqsubseteq x_n = \top\}

```

**Beispiel 3.3.2** Der binäre Verband  $\mathbf{B} = (\{\bot, \top\}, \bot, \top, \bot, \subset, \min, \max)$  ist distributiv und hat die Höhe height( $\mathbf{B}$ ) = 2.  $\mathbf{B}$  wird häufig in Datenflußanalysen benutzt. Ist eine Eigenschaft mit  $\top$  an einem Knoten gekennzeichnet, so hat sie dort Gültigkeit. Ungültige Aussagen über Eigenschaften werden mit  $\bot$  beschrieben.

#### 3.3.2 Transferfunktionen

Durch die Datenflußverbände werden Eigenschaften von Datenabhängigkeiten modelliert. Diese Eigenschaften verändern sich aber durch die Ausführung von Instruktionen. Daher wird ein Formalismus benötigt, der in der Lage ist, die durch die Programmausführung verursachten Veränderungen bzgl. der untersuchten Eigenschaften auf der Ebene der Datenflußverbände umzusetzen. Zu diesem Zweck werden Transferfunktionen definiert. Eigenschaften, die bei Erreichen eines Knoten gelten, müssen dies nicht auch bei Verlassen desselben tun, und umgekehrt. Damit modellieren Transferfunktionen die Semantik von Instruktionen in Bezug auf bestimmte Eigenschaften, wie z.B. die Veränderungen benutzter Variablen. Das Verhalten einer Sequenz von Instruktionen kann demnach durch fortgesetzte Anwendung der Transferfunktionen beschrieben werden.

Transferfunktionen sind Funktionen  $f: L \to L$ , die der Knotenmenge<sup>4</sup> des CFG FG=(N,E,s,e) zugeordnet sind:  $tf: N \to (L \to L)$ .

Die konkrete Definition einer Transferfunktion hängt von der zu beschreibenden Instruktion, den beteiligten Operanden und von der Art der zu untersuchenden Datenflußeigenschaften ab. Für Instruktionen ist es ausreichend zu beschreiben, wie sie auf ihre Operanden zugreifen. Es ist nicht wichtig, welche konkrete – z.B.

<sup>&</sup>lt;sup>4</sup>Transferfunktionen können auch den Kanten des CFG zugeordnet sein. Damit kann das Verhalten von verschiedenen Kanten, die einen Knoten erreichen, differenziert beschrieben werden.

arithmetische – Operation sie ausdrücken. Wird eine Variable gelesen, so ist dies ein Gebrauch, wird sie geschrieben, handelt es sich dabei um eine Definition. Ist es egal, ob es sich um einen Gebrauch oder eine Definition handelt, so wird der allgemeinere Begriff Referenz verwendet. Je nachdem, ob eine Referenz dafür sorgt, ob fortan eine bestimmte Eigenschaft gilt, oder eine Eigenschaft nicht mehr gilt, handelt sich dabei um eine erzeugende (generate) oder vernichtende (kill) Referenz. Anhand der Eigenschaft einer Instruktion, ob sie erzeugend oder vernichtend ist, die nicht nur von der Instruktion selbst, sondern auch von der Art der zu bestimmenden Information abhängig ist, kann dann die Transferfunktion festgelegt werden.

Monotonie ist für Transferfunktionen eine wichtige Eigenschaft, sowie auch die effektive Höhe eines Verbandes bzgl. einer Funktion. Beide dienen dazu, später Aussagen zur Terminierung und Zeitkomplexität von Datenflußanalysen machen zu können.

**Definition 3.3.5** Eine Funktion  $f: L \to L$  heißt monoton, wenn gilt:  $\forall x, y \in L: x \sqsubseteq y \Rightarrow f(x) \sqsubseteq f(y)$ .

**Definition 3.3.6** Die effektive Höhe eines Verbandes L bzgl. einer Funktion  $f: L \to L$  ist:

$$height_{eff}^{f}(L) = max\{n | \exists x_{1}, x_{2} = f(x_{1}), x_{3} = f(x_{2}), \dots, x_{n} = f(x_{n-1}) \in L : x_{1} \sqsubset x_{2} \sqsubset x_{3} \sqsubset \cdots \sqsubset x_{n} \sqsubseteq \top.$$

Mit der effektiven Höhe ist also die längste, streng monoton aufsteigende Kette iterierter Anwendungen der Funktion f gemeint.

**Definition 3.3.7** Sei  $\pi$  ein Pfad im CFG FG=(N,E,s,e) und seien  $n_1,\ldots,n_k$  die an  $\pi$  beteiligten Knoten in ihrer Ausführungsreihenfolge. Dann bestimmt sich die Transferfunktion des Pfades  $\pi$  durch  $f_{\pi} = f_{n_1} \circ \ldots \circ f_{n_k}$ .

Im allgemeinen ist ein Knoten n nicht nur über einen einzelnen Pfad zu erreichen, sondern es gibt mehrere Pfade, über die n von einem Startknoten aus zu erreichen ist. Daher ist eine Lösung anzustreben, die ein Erreichen eines Knoten n über alle Pfade ausdrückt. Je nach Zweck der späteren Verwendung liegt dabei das Interesse an der Erkundung aller Datenflußeigenschaften, die an Knoten n gelten  $k \ddot{o}nnen$  (may), oder an n gelten  $m \ddot{u}ssen$  (must). Der Unterschied entsteht dadurch, daß es potentielle und zwingende Gültigkeiten geben kann. Potentielle Gültigkeiten können aus der Lage von Instruktionen in nur einem von zwei möglichen Verzweigungsästen entstehen. Bei einer Programmausführung können wegen der Abarbeitung nur eines Verzweigungsastes Instruktionen unberücksichtigt bleiben. Sie könnten bei einer anderen Programmausführung aber durchaus durchgeführt werden. Alle potentiellen Gültigkeiten, die durch solche Situationen entstehen können, werden in der May-Lösung erfaßt. Werden alle zwingenden Gültigkeiten ermittelt, die unabhängig von einer konkreten Verzweigung Bestand haben, werden diese in der Must-Lösung

zusammengebracht. Es werden diejenigen Möglichkeiten ausgespart, die auf einigen - aber nicht allen - Pfaden zu n Gültigkeit erlangen.

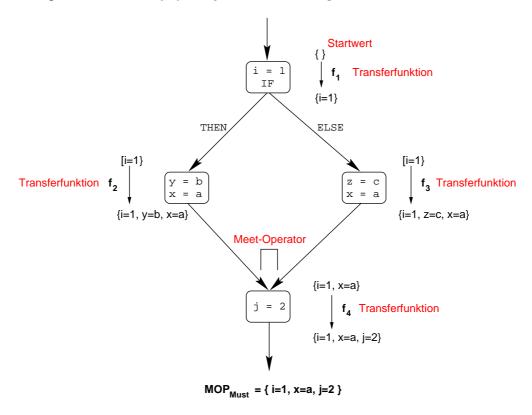

Beispiel 3.3.3 Datenflußanalyse zur Gewinnung von  $MOP_{Must}$

Das Beispiel 3.3.3 zeigt für einen Programmausschnitt mit einer Verzweigung die zwingenden Gültigkeiten beim Problem reaching definitions. Vom Startwert mit der leeren Menge aus werden für jeden Knoten Transferfunktionen auf die sie erreichenden Definitionen angewendet. Beim Zusammenführen von Kontrollflußpfaden wird ein Meet-Operator angewendet, der aus mehreren Mengen eine gemeinsam zwingend gültige Lösung bestimmt.

Entsprechend May oder Must gibt es zwei unterschiedliche Darstellungen<sup>5</sup>, die ausgehend von einem Startwert  $\iota$  die Gültigkeit an einem Knoten n bezeichnen.

• Sei für einen Knoten  $n \in N$  die Menge aller Pfade  $s \leadsto n$  gegeben durch  $\pi(n)$ . Die Merge-over-all-path (MOP)-Lösung für das May-Problem ist dann

$$MOP_{May}(n) = \bigsqcup_{p \in \pi(n)} f_p(\iota)$$

(3.1)

für einen Initialwert  $\iota \in L$ .

<sup>&</sup>lt;sup>5</sup>Gewöhnlich wird in der Literatur nur eine von beiden Lösungen dargestellt, ohne auf die andere hinzuweisen oder eine Unterscheidung anzugeben. Beim Zusammenführen mehrerer Quellen kann es daher Schwierigkeiten geben.

• Sei für einen Knoten  $n \in N$  die Menge aller Pfade  $s \rightsquigarrow n$  gegeben durch  $\pi(n)$ . Die Meet-over-all-path (MOP)-Lösung für das Must-Problem ist dann

$$MOP_{Must}(n) = \prod_{p \in \pi(n)} f_p(\iota)$$

(3.2)

für einen Initialwert  $\iota \in L$ .

## Beispiel 3.3.4 $MOP_{May}$ und $MOP_{Must}$

```

S_1: a = x+y;

S_2: if (k > 1)

S_3: b = x+1;

S_4: else c = y+1;

S_5: d = c+d;

```

- Analyse: Ausdrücke, die einen Knoten erreichen

- *Initialwert:*  $\iota = \{\}$

- $MOP_{May}(S_5) = \{x + y, k > l, x + 1, y + 1\}$

- $MOP_{Must}(S_5) = \{x + y, k > l\}$

Das Beispiel 3.3.4 zeigt für ein kurzes Programm diejenigen Ausdrücke, die das Statement  $S_5$  erreichen können oder müssen. Der Initialwert ist die leere Menge, da zu Beginn noch keine Ausdrücke ausgewertet vorliegen. Ausdrücke, die nur in einem Verzweigungsast vorkommen, erscheinen nur in der May-Lösung. Die Must-Lösung enthält nur die Ausdrücke, die unabhängig vom Verlauf der Verzweigung sind.

Die MOP-Lösungen enthalten die exakten Abhängigkeiten für alle Knoten n. Wenn die Transferfunktionen nicht monoton sind, oder es eine unendliche Anzahl verschiedener Pfade oder Elemente des Verbandes L gibt, sind die MOP-Lösungen nicht berechenbar. Das Problem der Bestimmung von Datenabhängigkeiten ist unentscheidbar. Wenn jedoch die Forderung nach exakter Bestimmung aller Datenabhängigkeiten fallengelassen wird, gibt es einen Ausweg. Wird einem Verfahren erlaubt, die Gültigkeit einer Aussage falsch zu bestimmen, d.h. fälschlicherweise Gültigkeit statt Ungültigkeit und umgekehrt zu berichten, so bestimmt es eine  $N\ddot{a}herungsl\ddot{o}sung$  oder Approximation der vollständig korrekten Lösung. Die Anzahl und die "Schwere" der Fehler eines Approximationsverfahrens lassen sich durch seine  $Pr\ddot{a}zision$  ausdrücken. Eine hohe Präzision ist erstrebenswert, denn damit wird die korrekte Lösung möglichst nahe erreicht.

### Beispiel 3.3.5 Approximation der $MOP_{Must}$ -Lösung

Zum Beispiel 3.3.4 könnte ein Verfahren folgende Approximationslösung für  $MOP_{Must}(S_5)$  liefern:  $MOP_{Must}(S_5) = \{x+y\}$ . Der Fehler, der gemacht wurde, liegt im "Unterschlagen" des Lösungsanteils k > l.

Neben der Präzision gibt es aber noch ein weiteres sehr wichtiges Merkmal einer Approximation, nämlich die Art der möglichen Fehler. Es bestehen die Möglichkeiten, eine gültige Aussage fälschlich als ungültig zu klassifizieren, oder eine ungültige Aussage als gültig zu bezeichnen. Wird in einer der Analyse folgenden Optimierung ein falsches Ergebnis genutzt, so kann das je nach Fehler dazu führen, daß eine mögliche Gelegenheit zur Optimierung nicht erkannt wird, oder schlimmer eine Optimierung durchgeführt, die zu semantisch inkorrektem Programmverhalten führt. Während ein Fehler der ersten Art "nur" die Effizienz eines Programms beeinflußt, Fehler der zweiten Art jedoch die Korrektheit, sind letztere unbedingt zu vermeiden. Um die geforderte Sicherheit zu gewährleisten, dürfen nicht beide Fehlerarten gleichzeitig auftreten. Für ein Must-Problem ist es daher besser, weniger Eigenschaften als zwingend (must) einzustufen als tatsächlich vorliegen. Die irrtümliche Klassifikation einer Eigenschaft als gültig, ist "gefährlich". Bei May-Problemen ist es umgekehrt. Hier ist es besser, mehr potentielle Gültigkeiten zu berichten, als eine Möglichkeit zu unterschlagen. Auch Aussagen zur Gültigkeit einer bestimmten Eigenschaft wie "unbekannt" sind besser als falsche Aussagen.

Die Beispiele 3.3.6 und 3.3.7 verdeutlichen die Wichtigkeit der Sicherheit von Approximationen. In Beispiel 3.3.6 wird der Ausdruck k>l fehlerhaft als nicht den Knoten  $S_5$  erreichend klassifiziert. Dadurch kann eine mögliche Gelegenheit zur Common Subexpression Elimination nicht erkannt werden. Die Folge ist, daß eine Optimierungsmöglichkeit "verschenkt" wird, das Programm bleibt aber korrekt. In Beispiel 3.3.7 wird durch die fehlerhafte Klassifizierung von y+1 bewirkt, daß eine CSE durchgeführt wird, die die Korrektheit des Programms zerstört.

**Beispiel 3.3.6** Verhinderung einer CSE-Optimierung durch eine sichere Approximation  $MOP_{Must}(S_5) = \{x + y\}$

```

Ursprüngl. Programm

Verpaßte Optimierung

S_1: a = x+y;

S_1: a = x+y;

S_2: if (k > 1)

S_2: if (t = (k > 1))

S_3: b = x+1;

S_3: b = x+1;

S_4: else c = y+1;

S_4: else c = y+1;

S_5: if (k > 1)

S_5: if (t)

```

**Beispiel 3.3.7** Fehlerhafte CSE-Optimierung durch eine unsichere Approximation  $MOP_{Must}(S_5) = \{x + y, k > l, y + 1\}$

```

\begin{array}{lll} \textit{Ursprüngl. Programm} & \textit{Fehlerhafte Optimierung} \\ S_1: \texttt{a} = \texttt{x+y}; & S_1: \texttt{a} = \texttt{x+y}; \\ S_2: \texttt{if (k > 1)} & S_2: \texttt{if (k > 1)} \\ S_3: & \texttt{b} = \texttt{x+1}; & S_3: & \texttt{b} = \texttt{x+1}; \\ S_4: \texttt{else c} = \texttt{y+1}; & S_4: \texttt{else t} = (\texttt{c} = \texttt{y+1}); \\ S_5: \texttt{x} = \texttt{y+1} & S_5: \texttt{x} = \texttt{t} \end{array}

```

Formal ergibt sich aus den Forderungen, daß eine sichere Approximation für ein Must-Problem eine Untermenge der MOP-Lösung sein muß, hingegen für ein May-Problem eine Obermenge der MOP-Lösung. Zum Beispiel 3.3.4 zeigt das folgende Beispiel 3.3.8 die Mengenbeziehungen zwischen der sicheren, der unsicheren und der exakten Lösung.

Beispiel 3.3.8 Sichere und unsichere Approximationen

```

• Exakte Lösung: MOP_{Must}(S_5) = \{x + y, k > l\}

```

```

• Sichere Approximation:

MOP_{Must}^{Approx}(S_5) = \{x + y\} \subset MOP_{Must}(S_5) = \{x + y, k > l\}

```

• Unsichere Approximation:  $MOP_{Must}^{Approx}(S_5) = \{x+y, k>l, y+1\} \not\subset MOP_{Must}(S_5) = \{x+y, k>l\}$

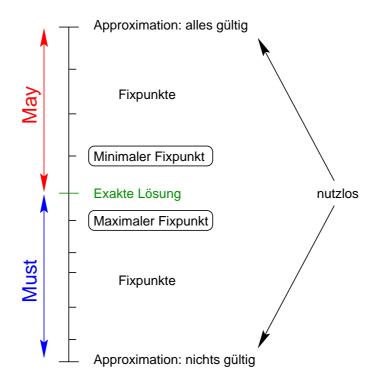

Sichere Approximationen lassen sich bestimmen, wenn die Höhe height(L) des verwendeten Datenflußverbandes beschränkt ist und die Transferfunktionen monoton sind [11]. Dann nämlich können ausgehend von Initialwerten fortlaufend die Transferfunktionen angewendet werden, bis sich nach einigen Iterationen die den Knoten zugeordneten Eigenschaftswerte nicht mehr verändern. Es ist ein Fixpunkt erreicht.

Im Eingangsbeispiel 3.3.1 wurde bereits, ohne die formalen Voraussetzungen zu haben, ein Fixpunkt berechnet. Dort wurde die Datenflußinformation solange von Knoten zu Knoten propagiert bis sich ein Zustand einstellte, bei dem sich die Ausdrucksmengen durch weitere Durchläufe nicht mehr änderten.

**Definition 3.3.8** Ein Fixpunkt einer Funktion  $f: L \to L$  ist ein Element  $x \in L$  mit f(x) = x.

Ein Fixpunkt ist eine Lösung eines Gleichungssystems aus Transferfunktionen. Jede weitere Anwendung einer Funktion verändert das Ergebnis nicht mehr. Das bedeutet, daß sich alle Abhängigkeiten (evtl. zyklisch) fortgepflanzt haben und sich das Gleichungssystem als ganzes stabilisiert hat. Damit verändern sich auch die Gültigkeiten der Datenflußeigenschaften nicht mehr, sie sind an allen Knoten bestimmt.

Zur Approximation der MOP-Lösung werden, ausgehend von einem Startwert, alle Transferfunktionen eines Pfades zu einem Knoten n solange angewendet, bis keine Veränderung der Lösungen mehr stattfindet. An Knoten zusammenlaufenden Kontrollflusses werden die Teillösungen wie folgt zusammengefaßt:

• Ein Minimaler Fixpunkt (MFP) für das May-Problem ist

$$MFP_{May}(n) = \begin{cases} \iota &, \text{ falls } n = s \\ \bigsqcup_{m \in pred(n)} f_n(n)(MFP(m)) &, \text{ sonst} \end{cases}$$

(3.3)

für einen Startwert  $\iota \in L$ .

• Ein Maximaler Fixpunkt (MFP) für das Must-Problem ist

$$MFP_{Must}(n) = \begin{cases} \iota &, \text{ falls } n = s \\ \prod_{m \in pred(n)} f_n(n)(MFP(m)) &, \text{ sonst} \end{cases}$$

(3.4)

für einen Startwert  $\iota \in L$ .

Abbildung 3.1: Exakte Lösung und Annäherungen durch Fixpunkte

Abbildung 3.3.2 zeigt die Bedeutung von Fixpunkten bei der Annäherung an die exakte Datenflußlösung. Um die exakte Lösung herum gibt es zwei Bereiche – den Bereich der Must-Lösungen und den Bereich der May-Lösungen. Obere Grenze der May-Lösungen ist der Punkt, an dem alle Aussagen als gültig erklärt werden. Der untere Grenze aller Must-Lösungen ist die leere Menge, es gelten keine Aussagen mehr. Sowohl alle Aussagen als gültig zu klassifizieren als auch keine Aussage zuzulassen, führt zu keinem Nutzen. Zwischen der oberen Grenzen (bzw. der unteren Grenze) unter der exakten Lösung liegen interessantere Bereiche für Approximationslösungen. Einzelne Lösungen sind Fixpunkte, bei denen alle Datenflußgleichungen erfüllt sind. Die Gesamtlösung ist stabil. Von mehreren möglichen Fixpunkten sind diejenigen die besten, die der exakten Lösungen so nahe wie möglich kommen. Für die May-Lösungen ist das der minimale Fixpunkt und für Must-Lösungen ist es der maximale Fixpunkt.

Zunächst ist jeder Fixpunkt eine Approximation der Lösung eines Datenflußproblems, denn für die o.g. Einschränkungen gilt:  $\forall n \in N : MOP_{Must}(n) \supseteq MFP_{Must}(n)$  bzw.  $\forall n \in N : MOP_{May}(n) \subseteq MFP_{May}(n)$ . Da aber auch die Güte der Approximation – die Präzision – für die weitere Verwendung wichtig ist, werden maximale bzw. minimale Fixpunkte angestrebt, die von allen Fixpunkten die größte Menge an Information zusammentragen. Wenn über die bisherigen Voraussetzungen hinaus, alle Transferfunktionen noch distributiv sind, dann ist die MOP-Lösung in diesem speziellen Fall berechenbar und es gilt:  $\forall n \in N : MFP(n) = MOP(n)$ .

Im folgenden beschäftigt sich diese Arbeit nur noch mit MFP-Lösungen. Dazu soll zunächst für den Fall der Datenabhängigkeiten zwischen skalaren Variablen gezeigt werden, wie zu einer solchen Lösung gelangt werden kann.

#### 3.3.3 Iterative Datenflußanalyse

Ein wichtiges und häufig verwendetes Verfahren ist die *iterative Datenflußanalyse*. Es stellt einen Algorithmus dar, der das Konzept der MFP-Lösungen für einen gegebenen CFG umsetzt.

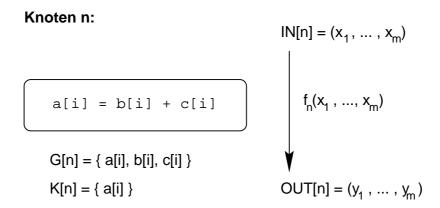

Sei nun dieser CFG FG = (N, E, s, e). Jedem Knoten n aus N werden zwei Werte  $IN[n], OUT[n] \in L$  zugeordnet. Diese bezeichnen die Datenflußinformation, die den Knoten n erreicht bzw. verläßt. Die Datenflußgleichungen für einen Knoten n zur Bestimmung des Must-Information sehen dann so aus:

$$IN[n] = \begin{cases} \iota &, \text{ falls } n = s \\ \bigcap_{m \in pred(n)} OUT[m] &, \text{ sonst} \end{cases}$$

(3.5)

$$OUT[n] = f_n(IN[n]) \tag{3.6}$$