# Das RICH-Multiplizitätsveto-System für das **HERA-B** Experiment

Vom Fachbereich Physik der Universität Dortmund zur

Erlangung des akademischen Grades eines Doktors der Naturwissenschaften genehmigte

#### **DISSERTATION**

von Diplom-Physiker Carsten Cruse

> Dortmund Oktober 2002

#### Gutachter:

- 1. Prof. Dr. P. Buchholz

- 2. Prof. Dr. D. Wegener

Tag der mündlichen Prüfung: 24.10.2002

### Inhaltsverzeichnis

| 1 | Einl | Einleitung |                                                                      |    |  |  |  |

|---|------|------------|----------------------------------------------------------------------|----|--|--|--|

| 2 | Das  | HERA       | -B Experiment                                                        | 5  |  |  |  |

|   | 2.1  |            | ERA-Speicherring                                                     | 5  |  |  |  |

|   | 2.2  | Die Ko     | omponenten des HERA-B Experiments                                    | 6  |  |  |  |

|   |      | 2.2.1      | Das Spurkammersystem                                                 | 8  |  |  |  |

|   |      | 2.2.2      | Detektoren zur Teilchenidentifikation                                | 9  |  |  |  |

|   | 2.3  | Das Tr     | riggersystem                                                         | 11 |  |  |  |

|   |      | 2.3.1      | Die Pretrigger                                                       | 14 |  |  |  |

|   |      | 2.3.2      | Die erste Triggerstufe (FLT)                                         | 17 |  |  |  |

|   |      | 2.3.3      | Das Datennahmesystem                                                 | 18 |  |  |  |

| 3 | Das  | Physil     | kprogramm von HERA-B                                                 | 19 |  |  |  |

|   | 3.1  | •          | Parton-Streuung                                                      | 19 |  |  |  |

|   | 3.2  |            | roduktionswirkungsquerschnitt der b-Quarks                           | 20 |  |  |  |

|   |      | 3.2.1      | Messung des Wirkungsquerschnitts $\sigma_{b\overline{b}}$ bei HERA-B | 22 |  |  |  |

|   | 3.3  | Quark      | onium-Produktion und nukleare Unterdrückung                          | 23 |  |  |  |

|   |      | 3.3.1      | Quarkonium-Produktion                                                | 24 |  |  |  |

|   |      | 3.3.2      | Nukleare Absorption                                                  | 26 |  |  |  |

|   |      | 3.3.3      | Potenzial von HERA-B                                                 | 27 |  |  |  |

|   | 3.4  | Zusam      | menfassung                                                           | 28 |  |  |  |

| 4 | Das  | RICH       | I-Veto-System                                                        | 31 |  |  |  |

|   | 4.1  |            | be des Veto-Systems                                                  | 31 |  |  |  |

|   |      | 4.1.1      | Physikalische Motivation                                             | 32 |  |  |  |

|   | 4.2  |            | zur Treffermultiplizität                                             | 36 |  |  |  |

|   |      | 4.2.1      | Datensätze der Studie                                                | 37 |  |  |  |

|   |      | 4.2.2      |                                                                      | 38 |  |  |  |

|   |      | 4.2.3      | Untersuchung der Treffermultiplizität der einzelnen Subdetektoren    | 38 |  |  |  |

|   |      | 4.2.4      | Untersuchungen zur Untergrundunterdrückung                           | 40 |  |  |  |

|   |      | 4.2.5      | Wahl des Detektorsystems zur Implementation des Multiplizi-          |    |  |  |  |

|   |      | 1.2.0      | tätsveto-Systems                                                     | 41 |  |  |  |

|   |      | 4.2.6      | Studie zur Untergrundunterdückung eines kombinierten ECAL-           |    |  |  |  |

|   |      | -          | RICH-Veto-Systems                                                    | 42 |  |  |  |

|   | 4.3  | Anford     | derungen an das RICH-Multiplizitätsveto-System                       | 42 |  |  |  |

|   |      | 4.3.1      | Das zum EEI komplementäre Entwicklungskonzept                        | 44 |  |  |  |

|   |     | 4.3.2                            | Schnittstelle zu den Pretriggern                                         |  |  |  |  |

|---|-----|----------------------------------|--------------------------------------------------------------------------|--|--|--|--|

|   |     | 4.3.3                            | Anforderung an die Latenzzeit des RICH-Multiplizitätsveto-Sys-           |  |  |  |  |

|   |     |                                  | tems                                                                     |  |  |  |  |

|   |     | 4.3.4                            | Technische Anforderungen                                                 |  |  |  |  |

|   | 4.4 | Aufba                            | u des RICH-Multiplizitätsveto-Systems                                    |  |  |  |  |

|   | 4.5 | Zusam                            | menfassung                                                               |  |  |  |  |

| _ | D   | 12 <b>C</b> D                    |                                                                          |  |  |  |  |

| 5 |     | I <sup>2</sup> C-B               |                                                                          |  |  |  |  |

|   | 5.1 |                                  | rs-Eigenschaften                                                         |  |  |  |  |

|   | 5.2 |                                  | C-Bus-Controller                                                         |  |  |  |  |

|   | - 0 | 5.2.1                            | Übertragungsmodi des I <sup>2</sup> C-Bus-Controllers                    |  |  |  |  |

|   | 5.3 |                                  | -Implementation des SLAVE-Controllers                                    |  |  |  |  |

|   |     | 5.3.1                            | CPLD-Implementation der Ansteuerung des I <sup>2</sup> C-Bus-Controllers |  |  |  |  |

|   |     | <b>.</b>                         | als SLAVE                                                                |  |  |  |  |

|   | _ , | 5.3.2                            | CPLD-Implementation des MASTER-Controllers                               |  |  |  |  |

|   | 5.4 |                                  | isation der Datenübertragung                                             |  |  |  |  |

|   |     | 5.4.1                            | Adressraumaufteilung des I <sup>2</sup> C-Busses                         |  |  |  |  |

|   |     | 5.4.2                            | Sende- und Empfangsablauf                                                |  |  |  |  |

|   | 5.5 | Modifi                           | kationen des I <sup>2</sup> C-Busses                                     |  |  |  |  |

|   | 5.6 | Test d                           | er Datenübertragung                                                      |  |  |  |  |

|   | 5.7 | Zusam                            | menfassung                                                               |  |  |  |  |

| 6 | Die | Base S                           | Sum Card                                                                 |  |  |  |  |

| Ū | 6.1 |                                  | eibung der Funktionalität der BSC                                        |  |  |  |  |

|   | 6.2 |                                  | eibung der Summationslogik                                               |  |  |  |  |

|   | 6.3 | Beschreibung der Summationslogik |                                                                          |  |  |  |  |

|   | 0.5 | 6.3.1                            | Beschreibung des Testprinzips                                            |  |  |  |  |

|   |     | 6.3.2                            | Beschreibung der Testmodule                                              |  |  |  |  |

|   |     | 6.3.2                            | Funktionstest der BSC mit Stimulusdateien                                |  |  |  |  |

|   |     |                                  |                                                                          |  |  |  |  |

|   |     | 6.3.4                            | Test der BSC mit Komponenten des HERA-B FED-Systems                      |  |  |  |  |

|   | C 1 | 6.3.5                            | Latenzzeitmessung                                                        |  |  |  |  |

|   | 6.4 | Zusam                            | menfassung                                                               |  |  |  |  |

| 7 | Die | FED S                            | Sum Card                                                                 |  |  |  |  |

|   | 7.1 | Beschr                           | eibung der Funktionalität der FSC                                        |  |  |  |  |

|   |     | 7.1.1                            | Programmierung der CPLDs                                                 |  |  |  |  |

|   |     | 7.1.2                            | Die Elektro / Opto-Wandlerschaltung                                      |  |  |  |  |

|   | 7.2 | Funkti                           | onstests der FSC                                                         |  |  |  |  |

|   |     | 7.2.1                            | Beschreibung der Testmodule                                              |  |  |  |  |

|   |     | 7.2.2                            | Beschreibung des Testaufbaus                                             |  |  |  |  |

|   |     | 7.2.3                            | Beschreibung der Funktionstests der FSC                                  |  |  |  |  |

|   |     | 7.2.4                            | Test der optischen Datenübertragung                                      |  |  |  |  |

|   | 7.3 |                                  | menfassung                                                               |  |  |  |  |

|   | 1.0 | ⊿ധാരവ⊔                           |                                                                          |  |  |  |  |

| 8   | Das            | Veto Board                                                                       | 93   |

|-----|----------------|----------------------------------------------------------------------------------|------|

|     | 8.1            | Beschreibung der Funktionalität des VBs                                          | 93   |

|     |                | 8.1.1 Programmierung des VME-CPLDs                                               | 96   |

|     |                | 8.1.2 Programmierung des Veto-CPLDs                                              | 96   |

|     | 8.2            | Funktionstest des VBs                                                            | 99   |

|     |                | 8.2.1 Beschreibung der Testmodule                                                | 99   |

|     |                | 8.2.2 Beschreibung des Testaufbaus                                               | 99   |

|     |                |                                                                                  | 100  |

|     |                | 8.2.4 Test der I <sup>2</sup> C-Bus-Schnittstelle und der Funktionalität des VBs |      |

|     |                | mit Komponenten des RICH-Multiplizitätsveto-Systems                              | 102  |

|     |                | 8.2.5 Latenzzeitmessung                                                          | 103  |

|     | 8.3            | <u> </u>                                                                         | 103  |

|     |                |                                                                                  |      |

| 9   | Der            | 8 88                                                                             | 107  |

|     | 9.1            |                                                                                  | 107  |

|     |                |                                                                                  | 109  |

|     | 9.2            | Das Fast Control System (FCS)                                                    | 113  |

|     |                | 9.2.1 Verarbeitung von Trigger-Signalen                                          | 113  |

|     |                | 9.2.2 Auslese der FED-Speicher                                                   | 114  |

|     |                | 9.2.3 Erzeugung der Testmuster                                                   | 114  |

|     | 9.3            |                                                                                  | 115  |

|     |                |                                                                                  | 115  |

|     |                | 9.3.2 Triggerkonfiguration März 2002                                             | 119  |

|     | 9.4            | Zusammenfassung                                                                  | 123  |

| 10  | TD 1           | 14. 4 1 1700 1 1 4.                                                              | 105  |

| 10  |                | 8                                                                                | 125  |

|     |                | v                                                                                | 125  |

|     | 10.2           | $ \mathcal{C} $                                                                  | 129  |

|     |                | 8                                                                                | 129  |

|     |                | <b>U</b>                                                                         | 129  |

|     | 400            | ı                                                                                | 129  |

|     | 10.3           | Zusammenfassung                                                                  | 134  |

| 11  | Zusa           | ammenfassung und Ausblick                                                        | 135  |

| A   | Abk            | ürzungsverzeichnis                                                               | 139  |

| D   | D:a            | Online Seft-ware des DICH Vete Systems                                           | 1 19 |

| Б   |                | Ų.                                                                               | 143  |

|     | $\mathbf{D.1}$ | Beschreibung der Online-Software                                                 | 144  |

| Lit | terat          | urverzeichnis                                                                    | 145  |

| Ind | dex            |                                                                                  | 153  |

| D٩  | nkes           | ogung                                                                            | 154  |

## Abbildungsverzeichnis

| 2.1  | Der HERA-Speicherring mit Vorbeschleunigern                                            | Ę          |

|------|----------------------------------------------------------------------------------------|------------|

| 2.2  | Der HERA – B Detektor                                                                  | 7          |

| 2.3  | Der RICH-Detektor                                                                      | 11         |

| 2.4  | Ein Ereignis im HERA-B Detektor                                                        | 12         |

| 2.5  | Das vierstufige Triggersystem                                                          | 13         |

| 2.6  | ECAL-Pretrigger und EEI                                                                | 15         |

| 2.7  | Der Myon-Pretrigger                                                                    | 16         |

| 2.8  | Das FLT-Netzwerk und zugehörige Detektorkomponenten                                    | 17         |

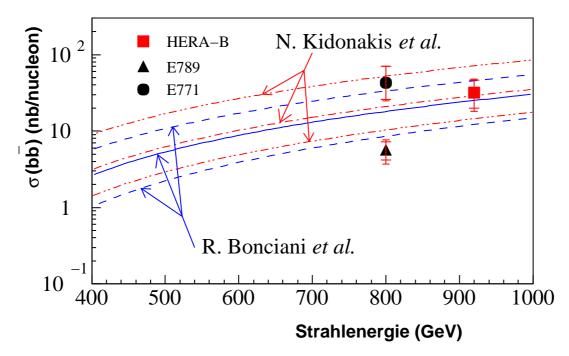

| 3.1  | Der Produktionswirkungsquerschnitt $\sigma(b\overline{b})$                             | 24         |

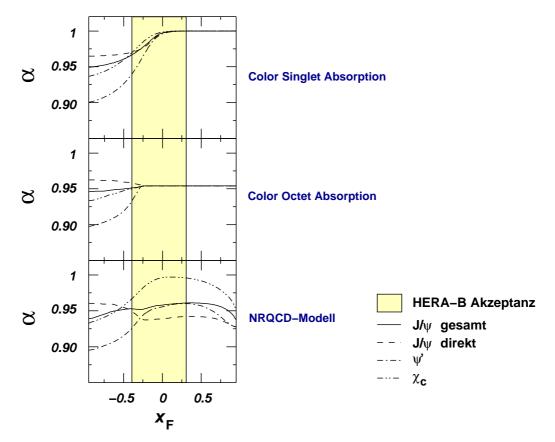

| 3.2  | Vorhersage zur Abhängigkeit der Unterdrückung unterschiedlicher Char-                  |            |

|      | moniumzustände von $x_{\rm F}$                                                         | 29         |

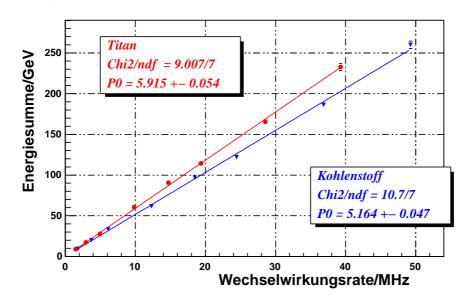

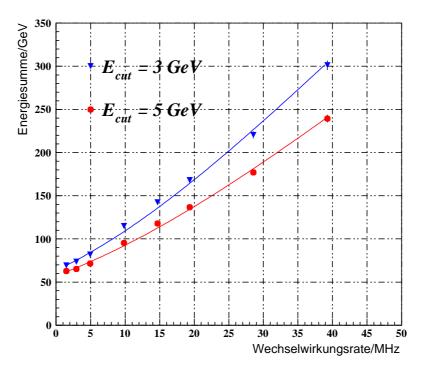

| 4.1  | ECAL-Energiesumme gegen Anzahl der Wechselwirkungen aufgetragen                        |            |

|      | (Monte Carlo)                                                                          | 33         |

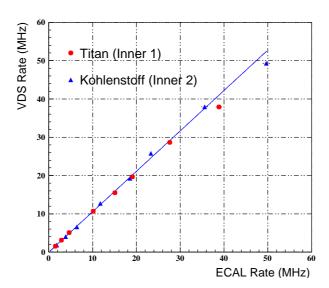

| 4.2  | ECAL-Energiesumme gegen Wechselwirkungsrate aufgetragen                                | 34         |

| 4.3  | ECAL-Energiesumme gegen Wechselwirkungsrate der Ereignisse mit ei-                     | 0.         |

| 4.4  | ner identifizierten Anzahl an Wechselwirkungen aufgetragen.                            | 35         |

| 4.4  | Vergleich der mit dem ECAL und mit dem VDS bestimmten Wechselwirkungsrate              | 36         |

| 4.5  | Subdetektoren der Multiplizitätsstudie                                                 | 37         |

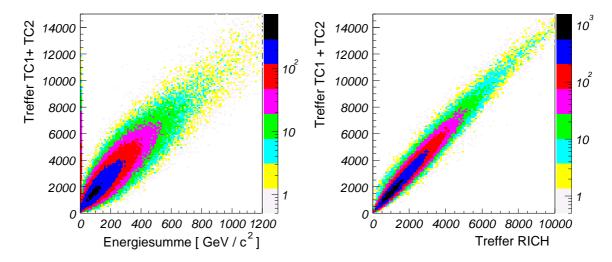

| 4.6  | Trefferkorrelation der unterschiedlichen Subdetektoren                                 | 39         |

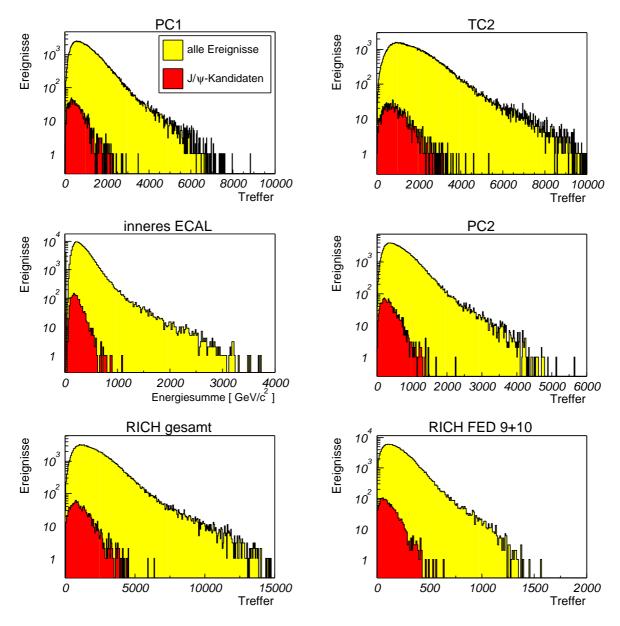

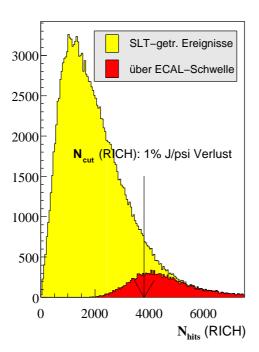

| 4.7  | Treffermultiplizität der unterschiedlichen Subdetektoren                               | 40         |

| 4.8  | Ereignisunterdrückung für ECAL-Energiesumme und Treffermultiplizitätsschwelle im RICH. | 43         |

| 4.9  | Schnittstellen zwischen RICH-Multiplizitätsveto-System und ECAL-Pre-                   |            |

|      | trigger                                                                                | 45         |

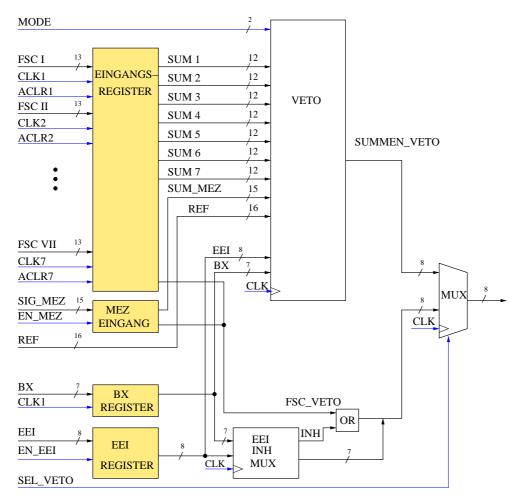

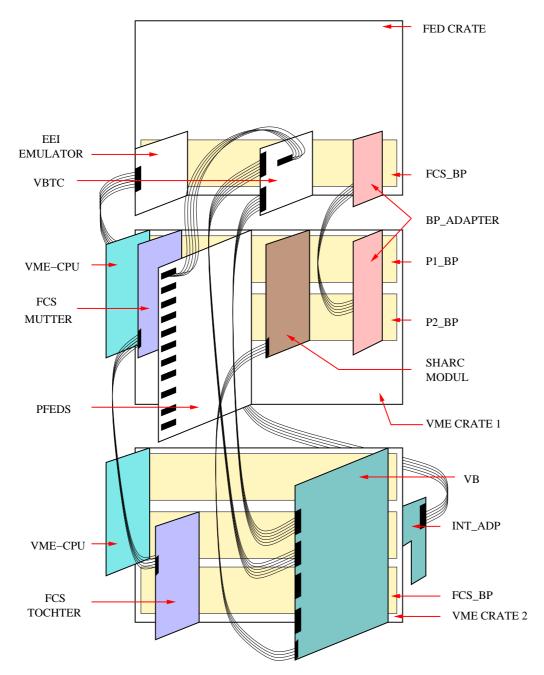

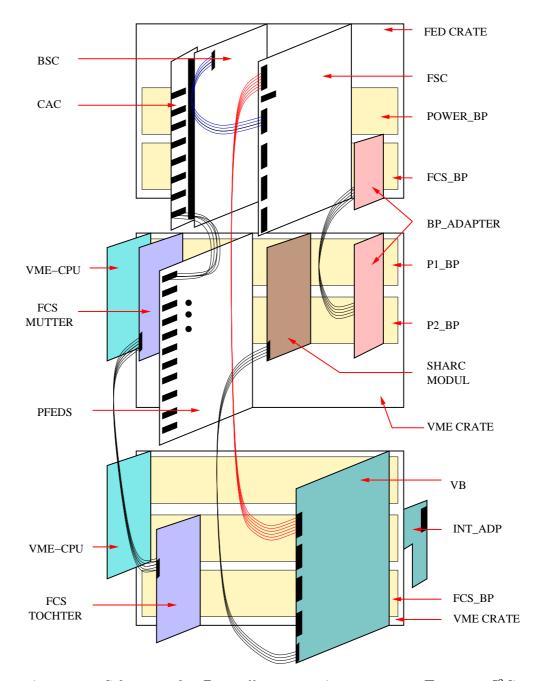

| 4.10 | Übersicht RICH-Multiplizitätsveto-System                                               | 49         |

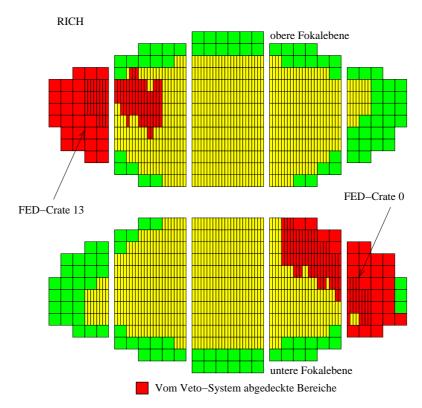

| 4.11 | Fokalebenen des RICH und Abdeckung durch das RICH-Multiplizitäts-                      | <b>.</b> . |

| 4.10 | veto-System                                                                            | 51         |

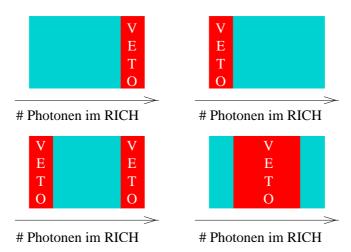

| 4.12 | Darstellung der einstellbaren Veto-Modi auf dem VB                                     | 52         |

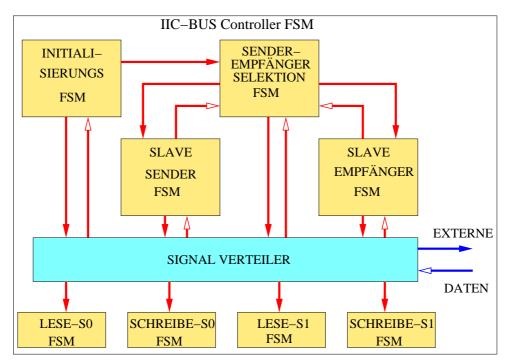

| 5.1  | Darstellung der I $^2$ C-Bus-Controller Zustandsmaschine                               | 58         |

| 5.2  | CPLD-Programmierung der SLAVE-Controller auf BSC und FSC                               | 60         |

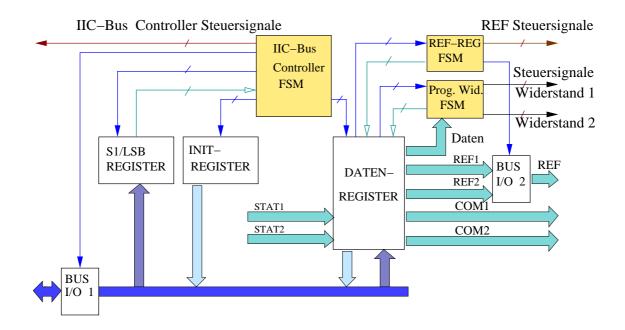

| 5.3  | Ansteuerung des MASTER I <sup>2</sup> C-Bus-Controllers                                | 61         |

| 5 4  | Modifikationen des I <sup>2</sup> C-Busses                                             | 64         |

| 5.5  | Oszilloskopaufnahme einer I <sup>2</sup> C-Busdatenübertragung im MASTER-Sendermodus des 4-Leitungsbetriebs                  | 65           |

|------|------------------------------------------------------------------------------------------------------------------------------|--------------|

| 5.6  | Oszilloskopaufnahme einer I <sup>2</sup> C-Bus Datenübertragung im MASTER-<br>Empfängermodus des 4-Leitungsbetriebs          | 66           |

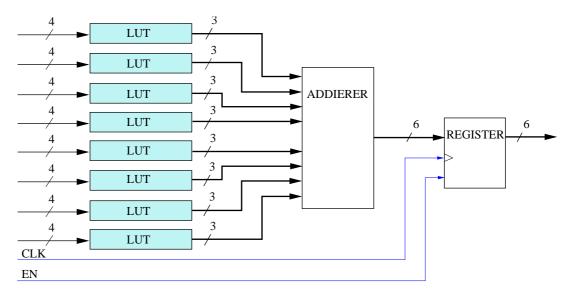

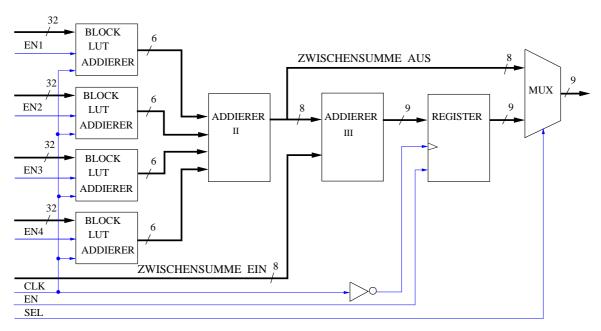

| 6.1  | Darstellung einer "Block LUT Addierer" Schaltung                                                                             | 71           |

| 6.2  | Summations-CPLD der BSC                                                                                                      | 72           |

| 6.3  | Testaufbau 1 für den BSC-Test                                                                                                | 7            |

| 6.4  | Testaufbau 2 für den BSC-Test                                                                                                | 76           |

| 6.5  | Platine BSC                                                                                                                  | 78           |

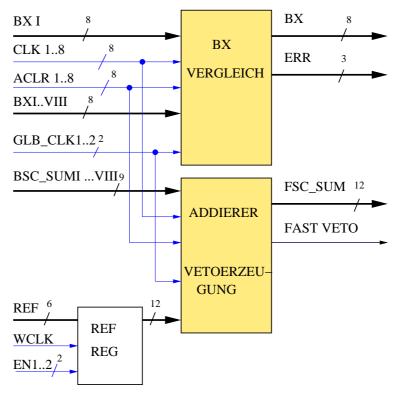

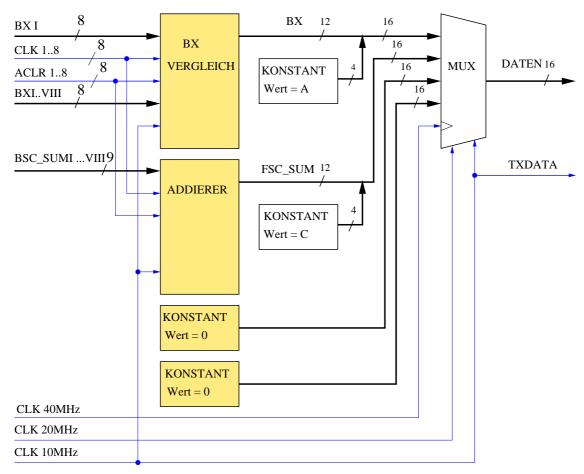

| 7.1  | FSC-CPLD-Programmierung (Flachkabelübertragung)                                                                              | 8            |

| 7.2  | FSC-CPLD-Programmierung (optische Übertragung)                                                                               | 84           |

| 7.3  | Testaufbau FSC-Test                                                                                                          | 86           |

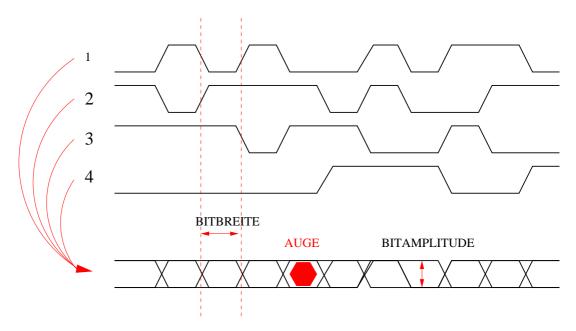

| 7.4  | Erläuterung der Augendiagramm-Darstellung                                                                                    | 89           |

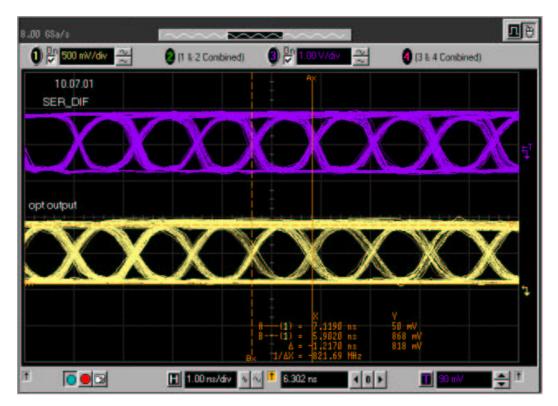

| 7.5  | Augendiagramme der optischen Übertragungsstrecke                                                                             | 90           |

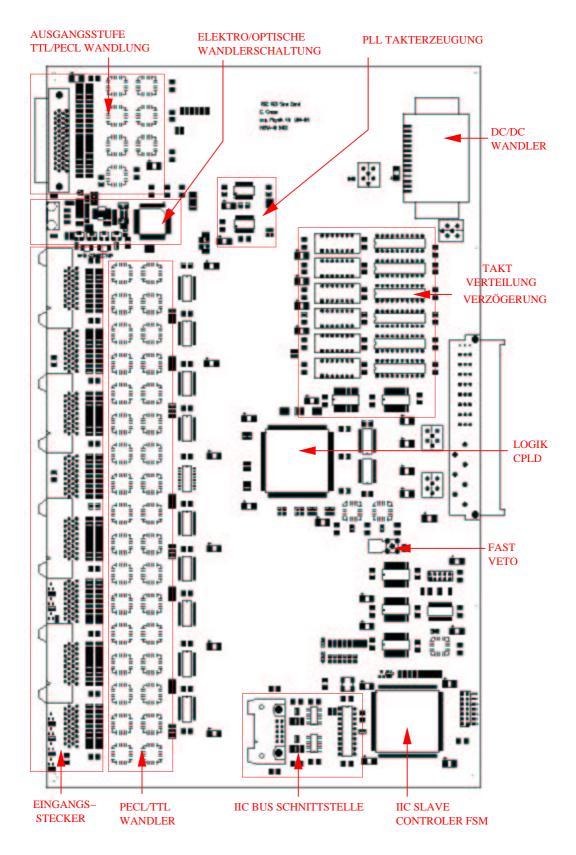

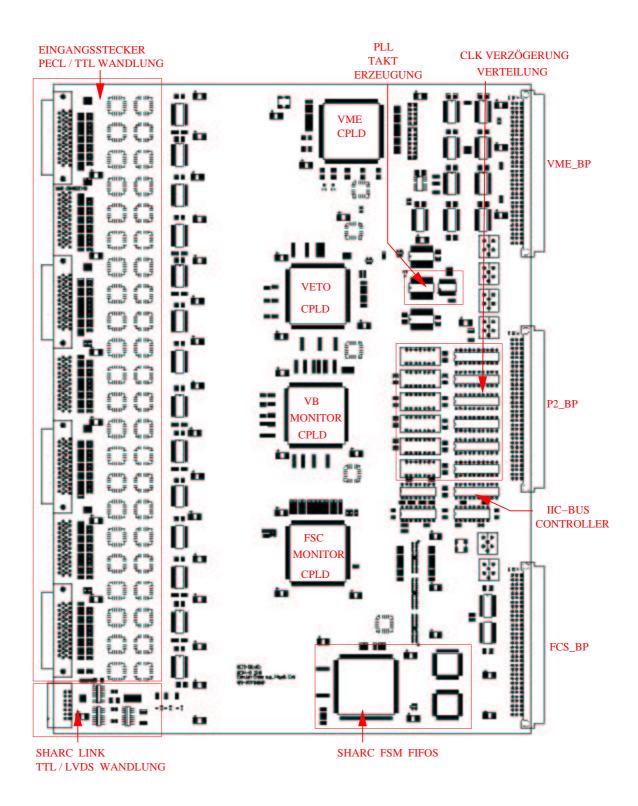

| 7.6  | Platine FSC                                                                                                                  | 9:           |

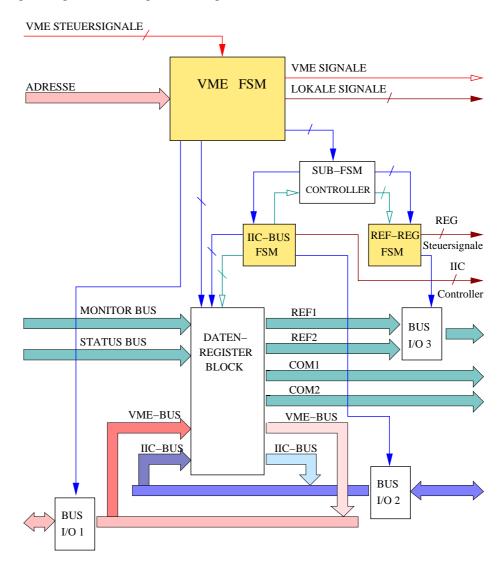

| 8.1  | Programmierung des VME-CPLDs                                                                                                 | 9            |

| 8.2  | Programmierung des Veto-CPLDs                                                                                                | 98           |

| 8.3  | Testaufbau 1 für den VB-Test                                                                                                 | $10^{\circ}$ |

| 8.4  | Testaufbau 2 für den VB-Test                                                                                                 | 10           |

| 8.5  | Platine VB                                                                                                                   | 100          |

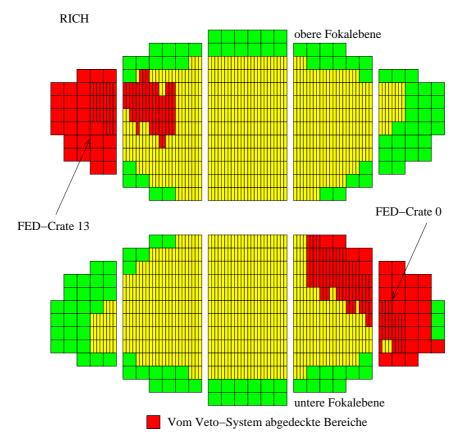

| 9.1  | Abdeckung der RICH-Fokalebenen durch das RICH-Multiplizitätsveto-<br>System                                                  | 108          |

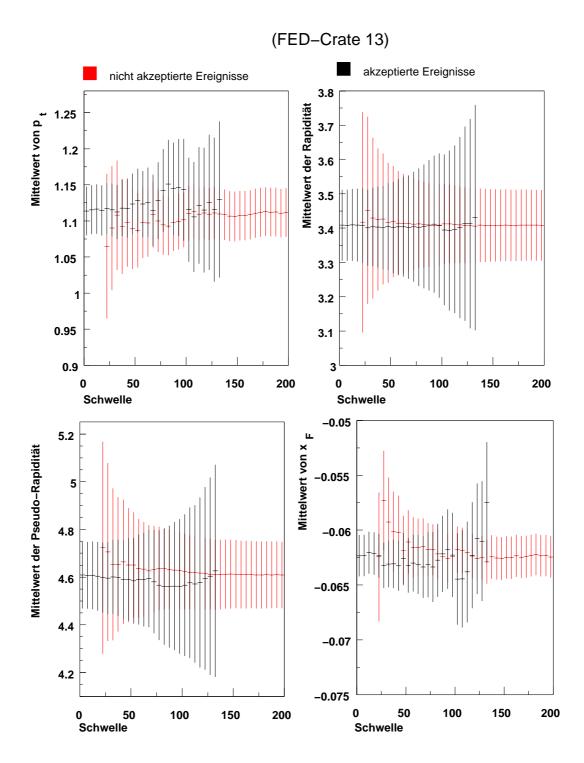

| 9.2  | Mittelwerte der Verteilungen der kinematische Variablen gegen die Multiplizitätsschwelle in einem RICH-FED-Crate aufgetragen | 11           |

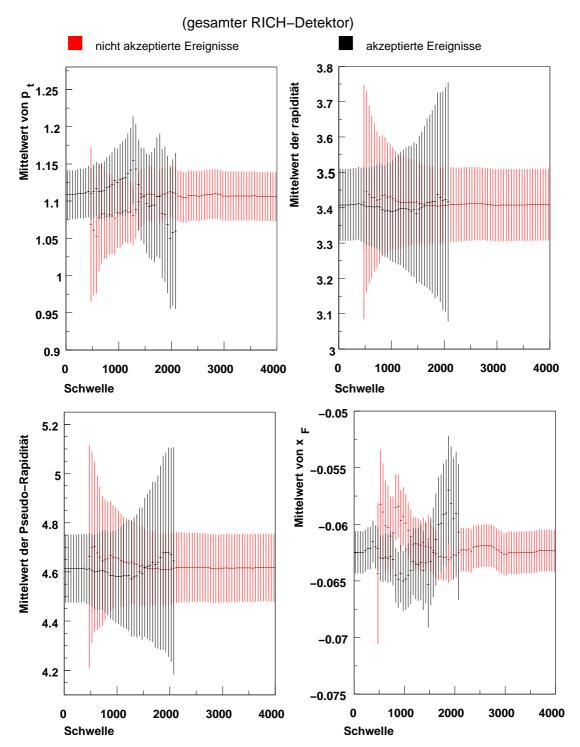

| 9.3  | Mittelwerte der Verteilungen der kinematische Variablen gegen Multi-                                                         | 110          |

| 0.4  | plizitätsschwelle im gesamten RICH-Detektor aufgetragen.                                                                     | 11:          |

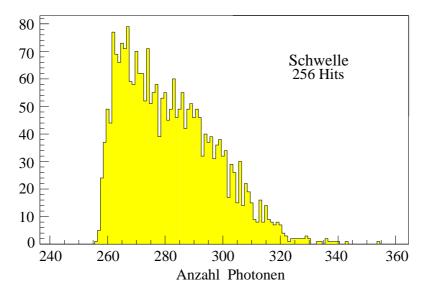

| 9.4  | Trefferhistogramm der Funktionsüberprüfung des Hardware-Wechselwirkungstriggers (LED-Pulse)                                  | 110          |

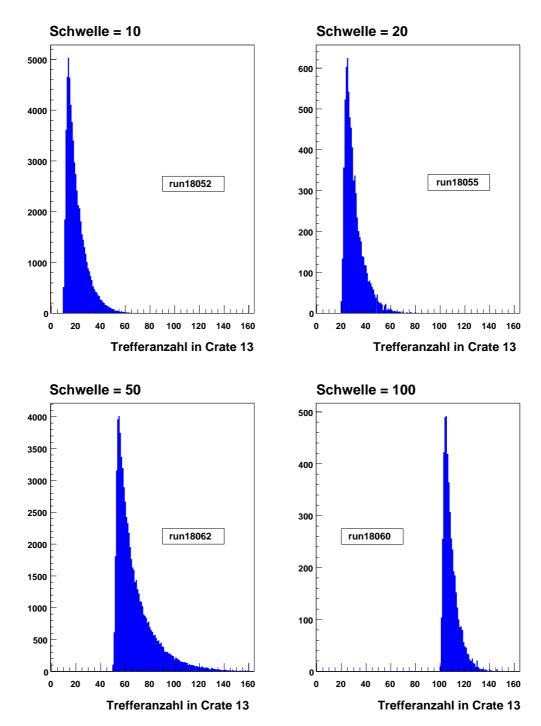

| 9.5  | Trefferhistogramme Hardware-Wechselwirkungstrigger FED-Crate 13, Da-                                                         |              |

|      | tennahme Dezember 2001                                                                                                       | 11'          |

| 9.6  | Trefferhistogramme Hardware-Wechselwirkungstrigger gesamter RICH,                                                            |              |

|      | Datennahme Dezember 2001                                                                                                     | 118          |

| 9.7  | Testaufbau des Systemtest in der HERA-B Umgebung                                                                             | 12           |

| 9.8  | Trefferhistogramme Hardware-Wechselwirkungstrigger, Datennahme Juli 2002                                                     | 123          |

| 10 1 | Funktionstests des RICH-Multiplizitätsveto-Systems und der Unterdrücku                                                       | nø           |

| 10.1 | der Pretrigger-Nachrichten an die erste Triggerstufe                                                                         | 120          |

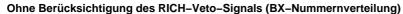

| 10.2 | Monitordaten des Myon-Pretriggers (BX-Nummernverteilung)                                                                     | 12           |

|      | Effizienzbestimmung des RICH-Multiplizitätsveto-Systems                                                                      | 13           |

|      | Trefferhistogramme zur Effizienzanalyse des RICH-Multiplizitätsveto-                                                         | 10           |

| 10.7 | Systems, Veto-Modus 0                                                                                                        | 13           |

| 10.5 | Trefferhistogramme zur Effizienzanalyse des RICH-Multiplizitätsveto-             |     |

|------|----------------------------------------------------------------------------------|-----|

|      | Systems, Veto-Modus 2                                                            | 133 |

| B.1  | Schematische Darstellung der Online-Umgebung des RICH-Multiplizitätsveto-Systems | 143 |

### **Tabellenverzeichnis**

| 1.1  | Fundamentale Wechselwirkungen im Standardmodell                                                                      | 1   |

|------|----------------------------------------------------------------------------------------------------------------------|-----|

| 1.2  | Elementare Fermionen im Standardmodell                                                                               | 2   |

| 4.1  | Korrelationskoeffizienten der Subdetektoren                                                                          | 39  |

| 4.2  | Untergrundunterdrückung für unterschiedliche Multiplizitätsschwellen .                                               | 41  |

| 4.3  | Untergrundunterdrückung des kombinierten ECAL-RICH-Veto-Systems                                                      | 43  |

| 4.4  | Zeitvorgabe des Myon-Pretrigger-System                                                                               | 47  |

| 4.5  | Zeitvorgabe des High- $P_T$ -Pretrigger-System                                                                       | 47  |

| 4.6  | Zeitvorgabe des ECAL-Pretrigger-Systems (EEI)                                                                        | 47  |

| 4.7  | Zeitvorgabe des ECAL-Pretrigger-Systems                                                                              | 48  |

| 4.8  | Latenzzeit des RICH-Multiplizitätsveto-Systems                                                                       | 53  |

| 9.1  | Prioritäten der Triggerquellen                                                                                       | 114 |

| 10.1 | ${\bf Datens\"{a}tze}\ {\bf zur}\ {\bf Effizienzanalyse}\ {\bf des}\ {\bf RICH-Multiplizit\"{a}tsveto-Systems}\ \ .$ | 130 |

| A 1  | Abkürzungsverzeichnis                                                                                                | 139 |

### Kapitel 1

### **Einleitung**

Das Ziel der Elementarteilchenphysik ist es, die elementaren Bestandteile und Wechselwirkungen der Materie zu untersuchen. Die bisher erfolgreichste Theorie zur Beschreibung der Bausteine der Materie und deren Wechselwirkungen ist das Standardmodell [Gla 61, Wei 67], das auf der Quantenmechanik [Pla 00, Sch 26, Hei 26] und der speziellen Relativitätstheorie [Ein 05] basiert. Das Standardmodell umfasst die vereinheitlichte Theorie der elektroschwachen Wechselwirkung [Gla 61, Sal 68, Wei 67, 't 72] und die Quantenchromodynamik (QCD)[GM64]. Im Folgenden wird ein kurzer Überblick über das Standardmodell gegeben.

Die Elementarteilchen werden in Fermionen und Bosonen unterteilt, die sich durch ihren Spin, eine quantenmechanische Eigenschaft, die kein mechanisches Analogon besitzt, unterscheiden. Der Spin der Fermionen beträgt  $\frac{\hbar}{2}$ , der der Bosonen ist  $\hbar$ . Die Fermionen werden weiterhin in Quarks und Leptonen unterteilt, auf die, nach der Beschreibung der fundamentalen Wechselwirkungen, eingegangen wird.

Tab. 1.1: Fundamentale Wechselwirkungen im Standardmodells

| Kraft             | Feldtheorie | Eichbosonen                     | Kopplung an     |

|-------------------|-------------|---------------------------------|-----------------|

| elektromagnetisch | QED         | Photon                          | elektr. Ladung  |

| schwach           | QFD         | W <sup>±</sup> , Z <sup>0</sup> | schwache Ladung |

| stark             | QCD         | 8 Gluonen                       | Farbladung      |

Neben der Gravitation, die nicht durch das Standardmodell beschrieben wird, existieren drei elementare Wechselwirkungen. Diese werden im Rahmen der Quantenfeldtheorie beschrieben, die auf dem Konzept von Eichsymmetrien mit lokaler Eichinvarianz beruht. Die Kräfte zwischen den Elementarteilchen werden durch den Austausch von Eichbosonen vermittelt. Die Quantenelektrodynamik (QED) [Fey 49, Sch 48, Tom 46] beschreibt die Wechselwirkung zwischen geladenenen Fermionen durch Austausch von Photonen. Die Quantenflavordynamik (QFD) [Fer 34] befasst sich mit der schwachen Wechselwirkung. Durch geladene Ströme der schwachen Wechselwirkung lassen sich Quarks in andere Quarks und Leptonen in andere Leptonen überführen. Die QED und die QFD konnten in eine einheitliche elektroschwache Theorie zusammengefasst

werden. Quarks besitzen einen weiteren Freiheitsgrad, der Farbladung genannt wird. In der Quantenchromodynamik wird die starke Wechselwirkung farbgeladener Quarks durch den Austausch von Gluonen formuliert. Die Gluonen tragen selber Farbladung und können daher untereinander wechselwirken. Die Austauschteilchen der schwachen Wechselwirkung koppeln über die Quantenzahl des schwachen Isospins ebenfalls aneinander. In Tabelle 1.1 sind die fundamentalen Wechselwirkungen und die Austauschteilchen aufgelistet.

Tab. 1.2: Elementare Fermionen im Standardmodells. Zu jeder der drei Familien gehören zwei Quarks und zwei Leptonen. Die Antiteilchen sind nicht aufgelistet.

| Generation | Quark          |            | Lepton                    |                        |

|------------|----------------|------------|---------------------------|------------------------|

| 1          | Up<br>D        | (u)        | Elektron-Neutrino         | $(\nu_e)$              |

| 2          | Down<br>Charm  | (d)<br>(c) | Elektron<br>Myon-Neutrino | $(e)$ $(\nu_{\mu})$    |

| 3          | Strange<br>Top | (s)<br>(t) | Myon<br>Tau-Neutrino      | $(\mu)$ $(\nu_{\tau})$ |

| 0          | Bottom         | (b)        | Tau                       | $(\tau)$               |

Neben den Eichbosonen gibt es die bereits erwähnten Quarks und Leptonen. Sie lassen sich in drei Familien oder Generationen anordnen, die ähnliche Eigenschaften besitzen. In Tabelle 1.2 sind die Fermionenfamilien dargestellt. Zu jedem Fermion existiert ein Antiteilchen, das die gleichen Quantenzahlen wie das Fermion besitzt, mit Ausnahme der ladungsartigen Quantenzahlen, deren Vorzeichen umgekehrt sind.

Die Voraussagen des Standardmodells der Elementarteilchenphysik wurden in einer Reihe von komplementären Experimenten überprüft. Die Messungen stimmen mit den Voraussagen in hoher Präzision überein [Gur 00, Erl 00, Ynd 02]. Trotzdem existieren einige offene Fragen, die vom Standardmodell nicht beantwortet werden. Eine der ungeklärten Fragen ist die Einbeziehung der Gravitation in eine konsistente Beschreibung der Phänomene im energetischen Bereich der Planckskala, in dem die Gravitationskraft nicht mehr vernachlässigt werden kann. Zusätzlich existieren freie Parameter, wie die Massen der Fermionen und Eichbosonen, die Koeffizienten der Kobayashi-Maskawa-Matrix, die die Kopplungen der Quarks untereinander beschreibt, und die Werte der Kopplungskonstanten. Diese Parameter können nicht aus den fundamentalen Prinzipien abgeleitet, sondern müssen experimentell bestimmt werden. Die jüngsten Resultate des SNO¹-Experiments [Hee 01] haben ergeben, dass die Neutrinos, im Gegensatz zu den Annahmen im Standardmodell, eine endliche Ruhemasse besitzen müssen.

Das Standardmodell stellt daher nicht die endgültige Theorie zur Beschreibung der Elementarteilchenphysik dar. Die Suche nach einer einheitlichen Theorie wird die Physiker auch weiterhin beschäftigen.

<sup>&</sup>lt;sup>1</sup>Sudbury Neutrino Observatory

#### Ziele dieser Arbeit

Das HERA-B Experiment am Deutschen Elektronen-Synchrotron (DESY) wurde zur Untersuchung der B-Mesonen-Physik aufgebaut. Im Gegensatz zu den Experimenten BABAR [Bou 95] in den USA und BELLE [Che 95] in Japan, die B-Mesonen-Physik an e<sup>+</sup>e<sup>-</sup>-Speicherringen untersuchen, verwendet HERA-B ein feststehendes Target, in dem Protonen mit einer Energie von 920 GeV mit den Nukleonen des Targetmaterials zur Wechselwirkung gebracht werden. Da HERA-B ein Hochratenexperiment ist, das Wechselwirkungsraten besitzt, wie sie die LHC<sup>2</sup> Experimente haben werden, ist der Anspruch an die Subdetektoren und das Triggersystem viel höher als bei den Experimenten BABAR und BELLE. Die hohe Datenrate impliziert, dass es nicht möglich ist, die Daten aller Ereignisse auszulesen und zu analysieren. Ein effektives Triggersystem wird benötigt, um die physikalisch relevanten Ereignisse zu selektieren. Es muss einen Unterdrückungsfaktor in der Größenordnung 10<sup>6</sup> liefern. Das hochgradig komplexe Triggersystem des HERA-B Experiments ist vierstufig aufgebaut, wobei die erste Triggerstufe rein hardwarebasiert arbeitet. Schon in der ersten Triggerstufe werden für sämtliche Ereignisse Spuren rekonstruiert, Spurparameter berechnet und Schnitte auf physikalisch relevante Parameter durchgeführt, um eine Unterdrückung um einen Faktor 200 zu erreichen.

Die hohe Ereignis- und Teilchenrate führte zu unvorhergesehenen technischen Problemen bei der Inbetriebnahme des Triggers und der Spurkammern, was zu einer Verzögerung des Beginns der Datennahme führte. HERA-B konnte daher keinen konkurenzfähigen Beitrag auf dem Gebiet der B-Mesonen-Physik liefern. Das Physikprogramm von HERA-B wurde neu ausgerichtet und befasst sich nun mit der Überprüfung einiger Aspekte der QCD, die erstmals mit dem HERA-B Detektor untersucht werden können. Das Programm wird in Kapitel 3 ausführlich erläutert.

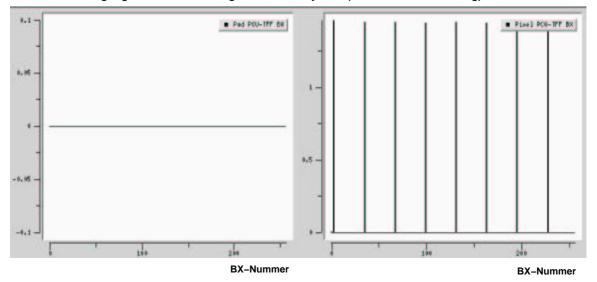

Im Rahmen dieser Arbeit wurde ein RICH-Multiplizitätsveto-System entwickelt, das Ereignisse mit einer zu großen Treffermultiplizität in den von der ersten Triggerstufe benutzten Detektorlagen unterdrückt, bevor diese vom Triggersystem verarbeitet werden. Ereignisse mit zu großer Treffermultiplizität belasten die Datenverarbeitung des Triggers und führen zu einem Anstieg der Latenzzeit. Daraus kann ein Ereignisverlust resultieren, da der ersten Triggerstufe nur 12  $\mu$ s zur Entscheidungsfindung zur Verfügung stehen, bevor die Daten verloren gehen. Durch das RICH-Multiplizitätsveto-System wird der Trigger entlastet, da alle Ereignisse mit einer zu großen Treffermultiplizität unterdrückt werden. Aufgrund des Spurfindungsalgorithmus werden von der ersten Triggerstufe bevorzugt Ereignisse mit hoher Treffermultiplizität selektiert. Eine hohe Treffermultiplizität resultiert aus einer großen Anzahl gleichzeitiger Wechselwirkungen. Rekonstruktionsbedingt lassen sich jedoch nicht mehr als drei bis vier gleichzeitige Wechselwirkungen untersuchen, da die Detektorauflösung für eine höhere Anzahl nicht ausreicht. Das RICH-Multiplizitätsveto-System trägt daher zur Verbesserung der Reinheit der Daten bei, indem Ereignisse mit zu vielen gleichzeitigen Wechselwirkungen unterdrückt werden.

Das Veto-System kann auch als nicht verzerrender Hardware-Wechselwirkungstrigger benutzt werden. In diesem Betriebsmodus wird eine Mindestanzahl Photonen im RICH-Detektor gefordert. Mit dem Hardware-Wechselwirkungstrigger bietet sich die Möglich-

<sup>&</sup>lt;sup>2</sup>Large Hadron Collider

keit, unabhängig vom Triggersystem, Daten zur Inbetriebnahme anderer Subdetektore zu nehmen. Im Rahmen einer begleitenden Diplomarbeit [Brü 02e] wurden Effizienzanalysen durchgeführt. Die Ergebnisse der Analysen werden ebenfalls zusammengefasst dargestellt.

Das RICH-Multiplizitätsveto-System ist ein komplexes Hardware-System, das modular aufgebaut und rein digital realisiert ist. Der Großteil der Schaltungen ist in programmierund rekonfigurierbaren Bausteinen implementiert, wodurch das System sehr flexibel für zukünftige Anpassungen bzw. Änderungen ist. Die Datenverarbeitung des Veto-Systems ist trotz der digitalen Realisierung der Schaltungen so schnell, dass die Nachrichten der Pretrigger an die ersten Triggerstufe unterdrückt werden. Ein Monitorsystem ermöglicht die Überprüfung von Hardware-Funktionen während des Betriebs. Die Anforderungen an das RICH-Multiplizitätsveto-System werden ausführlich in Kapitel 4 erläutert. Das Veto-System wurde unter enormem Zeitdruck entwickelt, getstet, im HERA-B Experiment installiert und in Betrieb genommen.

Der Aufbau der Arbeit gliedert sich wie folgt:

Im zweiten Kapitel wird der HERA-B Detektor beschrieben. Ausgehend von den messtechnischen Möglichkeiten des HERA-B Detektors wird im dritten Kapitel das neu ausgerichtete Physikprogramm erläutert. Das vierte Kapitel liefert eine Übersicht zu den physikalischen Aspekten des Veto-Systems und legt die Beweggründe dar, den RICH-Detektor zur Implementation des Veto-Systems zu benutzen. Anschließend wird das RICH-Multiplizitätsveto-System kurz vorgestellt. In den nachfolgenden vier Kapiteln werden die Module des RICH-Multiplizitätsveto-Systems detailliert dargestellt, die Testprozeduren beschrieben und Testergebnisse präsentiert. Das neunte Kapitel beschäftigt sich mit dem Betriebsmodus als nicht verzerrender Hardware-Wechselwirkungstrigger. Im zehnten Kapitel werden Ergebnisse der Effizienzanalysen gezeigt.

### Kapitel 2

### Das HERA-B Experiment

HERA-B ist eines der vier Experimente am HERA<sup>1</sup>-Speicherring des Deutschen Elektronen-Synchrotron (DESY) in Hamburg. In diesem Kapitel wird der HERA-B Detektor beschrieben, wobei dem RICH-Detektor, dem Triggersystem und dem Datennahmesystem besondere Beachtung gewidmet wird, da diese Subsysteme für das RICH-Multiplizitätsveto-System von besonderer Bedeutung sind.

#### 2.1 Der HERA-Speicherring

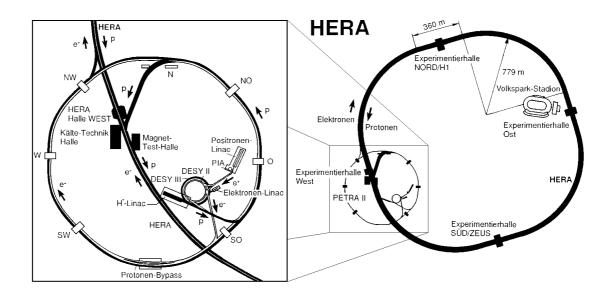

Abb. 2.1: Der HERA-Speicherring am  $\mathbf{DESY}$  und seine Vorbeschleuniger [DES 00].

Der HERA-Speicherring besteht aus einem Protonen- und einem Elektronen-Speicherring. Die Speicherringe besitzen einen Umfang von 6,3 km. Protonen und Elektronen

$<sup>^1</sup>$  Hadron-Elektron-Ring-Anlage

bzw. Positronen umlaufen den Speicherring in entgegengesetzten Richtungen. Die Protonen werden auf eine Energie von 920 GeV und die Elektronen² auf eine Energie von 27,5 GeV beschleunigt. Eine Übersicht über den HERA-Speicherring und seine Vorbeschleuniger ist in Abbildung 2.1 zu sehen. Es existieren vier Wechselwirkungszonen, in denen sich die Experimente H1 (Experimentierhalle NORD), HERMES (Experimentierhalle OST), ZEUS (Experimentierhalle SÜD) und HERA-B (Experimentierhalle WEST) befinden. H1 [Abt 93] und ZEUS [ZEU 86] erforschen die Struktur des Protons in Elektron-Proton-Streuexperimenten. Das HERMES Experiment [HER 90] untersucht die Spin-Struktur des Protons. Der polarisierte Elektronenstrahl wird dazu mit einem polarisierbaren Gas-Target zur Wechselwirkung gebracht. Das HERA-B Experiment [Loh 94] ist ebenfalls als Fixed-Target³-Experiment aufgebaut, benutzt jedoch nur die Protonen des Protonenstrahls, um diese mit mehreren Draht-Targets zur Wechselwirkung zu bringen.

Die Teilchenstrahlen in den Speicherringen bestehen nicht aus kontinuierlichen Strahlen, sondern sind in Pakete (Bunch) mit 5-7·10<sup>10</sup> Teilchen aufgeteilt. Es können 220 Pakete in die Speicherringe eingefüllt werden. Der zeitliche Abstand zwischen den Paketen beträgt 96 ns, was einer Rate von 10,416 MHz entspricht. In dem Protonen-Speicherring sind nur 180 der 220 Pakete mit Protonen gefüllt, woraus sich eine mittlere Rate gefüllter Protonen-Pakete von 8,5 MHz ergibt. Passiert ein Protonen-Paket das Target des HERA-B Experiments, wird dies als Bunch Crossing (BX) bezeichnet. Im HERA-B Experiment werden die Daten der Ereignisse, die während eines BX stattfinden, mit einer Markierung versehen, die BX-Nummer genannt wird.

#### 2.2 Die Komponenten des HERA-B Experiments

Das HERA-B Experiment ist als Vorwärts-Spektrometer mit einer hohen Akzeptanz, einer Abdeckung von 90 % des Raumwinkels im Schwerpunktsystem der Proton-Nukle-on-Wechselwirkung, aufgebaut. Die Protonen des äußeren Bereichs des Protonstrahls werden mit den Nukleonen von bis zu acht Draht-Targets zur Wechselwirkung gebracht [Ehr 00]. Die Draht-Targets sind in zwei Stationen zu jeweils vier Drähten angeordnet, die einen Abstand von 5 cm voneinander haben. Dadurch lassen sich, auch bei mehr als einer Wechselwirkung pro BX, die Vertices separieren. Die Drähte besitzen eine Ausdehnung von 50  $\mu$ m transversal und 50–500  $\mu$ m longitudinal zum Strahl. Sie lassen sich zum Strahl hin- oder von ihm wegbewegen. Eine automatische Steuerung [İşse 01] kontrolliert die Target-Positionen, um eine stabile Target-Rate zu gewährleisten.

Das HERA-B Experiment wurde entwickelt und aufgebaut, um die CP-Verletzung im System der B-Mesonen zu messen. Die Detektorkomponenten und das Triggersystem sind daher zum Nachweis von Teilchen mit hohem Transversalimpuls optimiert. Das b-Quark, das bei der Proton-Nukleon-Wechselwirkung erzeugt wird, ist viel schwerer als andere erzeugte Teilchen. Die Zerfallsprodukte des b-Quarks besitzen daher hohe Impulse bzw. Transversalimpulse. Die Sekundärvertices der B-Mesonen sind aufgrund der Lebensdauer der B-Mesonen klar von den Primärvertices separiert. Die Zerfallskaskaden der B-Mesonen, in denen Leptonen bzw. Leptonenpaare entstehen, sind re-

<sup>&</sup>lt;sup>2</sup>Im Weiteren wird Elektronen synonym für Elektronen und Positronen verwendet.

<sup>&</sup>lt;sup>3</sup>engl. für festes Ziel

lativ einfach zu identifizieren. Die Signatur der Myonen ist besonders gut für die Rekonstruktion geeignet, da sie sich gut vom hadronischen Untergrund separieren läßt. Der Wirkungsquerschnitt zur Erzeugung von bb-Paaren liegt bei ca. 30 nb / Nukleon (siehe auch Kapitel 3), während der gesamte inelastische Wirkungsquerschnitt bei ca. 10 mb / Nukleon liegt [Loh 94]. Das Triggersystem muss also eine Untergrundunterdrückung in der Größenordnung von  $10^{-6}$  liefern.

Für die Rekonstruktion der Wechselwirkungen müssen die Eigenschaften sämtlicher Zerfallsprodukte gemessen werden. Das HERA-B Experiment hat daher fünf Aufgaben zu erfüllen:

- 1. Rekonstruktion des Herkunftsortes der Zerfallsprodukte,

- 2. Impuls- und Bahnrekonstruktion der Zerfallsprodukte,

- 3. Teilchenidentifikation,

- 4. Energiemessung,

- 5. Bereitstellung eines schnellen und effektiven Triggersystems.

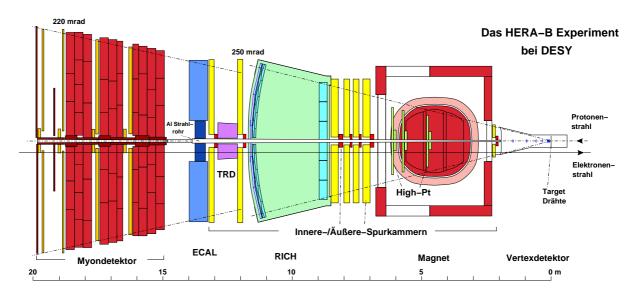

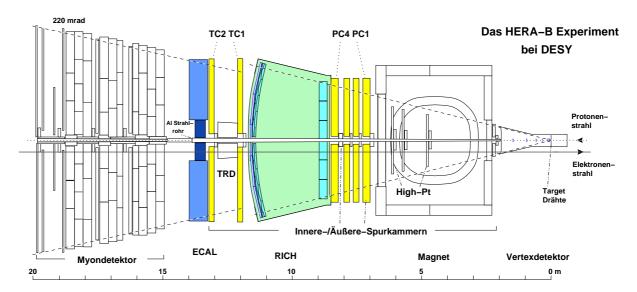

Um diese Aufgaben zu erfüllen, besitzt das HERA-B Experiment, schematisch in Abbildung 2.2 dargestellt, einen Vertexdetektor, ein Spurkammersystem und Subdetektoren zur Teilchenidentifizierung. Das Triggersystem ist vierstufig aufgebaut. Im Folgenden werden die einzelnen Subdetektorkomponenten erläutert. Die Orientierung des Koordinatensystems ist wie folgt: die positive x-Achse zeigt in Richtung des Speicherringzentrums, die positive z-Achse weist in Flugrichtung der Protonen, die positive y-Achse steht senkrecht auf der x-z-Ebene und weist nach oben.

Abb. 2.2: Schematische Darstellung des HERA-B Detektors in der Aufsicht (nach [Loh 94]).

#### Vertex-Detektor-System (VDS)

Die Hauptaufgabe des VDS [Bau 00] (in Abbildung 2.2 mit Vertexdetektor bezeichnet) ist es, die Primärvertices der Wechselwirkungen auf den Target-Drähten sowie die Sekundärvertices zu rekonstruieren. Der VDS besteht aus acht Superlagen doppelseitiger Siliziumstreifendetektoren. Jede Superlage ist aus zwei um 5° gegeneinander verdrehten Lagen aufgebaut. Dies ermöglicht eine dreidimensionale Rekonstruktion der Spuren. Die acht Superlagen sind in einem Abstand von 5,5 cm bis 2,07 m hinter dem Target angeordnet. Sie decken einen Raumwinkel von 10-250 mrad ab. Die Auflösung transversal zur Strahlrichtung liegt bei  $\sigma_{tran}=80\,\mu\text{m}$ , in longitudinaler Richtung beträgt sie  $\sigma_{long}=600\,\mu\text{m}$ . Dies ist ausreichend, um die Sekundärvertices z. B. der B-Mesonen, die aufgrund der Lebensdauer der B-Mesonen von 1,5 ps ca. 10 mm vom Primärvertex separiert sind, aufzulösen.

#### 2.2.1 Das Spurkammersystem

Das Spurkammersystem hat die Aufgabe, Teilchenspuren zwischen VDS und den weiter entfernten Detektoren zur Teilchenidentifikation zu rekonstruieren. Die Teilchenflussdichte nimmt mit dem Abstand R zum Protonstrahl proportional zu  $\sim 1/R$  ab. Dies wird durch unterschiedliche Granularitäten der verwendeten Detektortypen berücksichtigt. Das Spurkammersystem ist in einen inneren Bereich hoher Granularität, nahe des Strahlrohres, und einen äußeren Bereich niedrigerer Granularität unterteilt.

#### Innere Spurkammern (ITR)

Die inneren Spurkammern [Zeu 00] bestehen aus Mikrostreifen-Gas-Detektoren mit Gas-Elektronen-Vervielfacher-Folien (GEM-MSGC). Es existieren sieben Superlagen. Eine befindet sich vor dem Magneten, vier zwischen Magnet und RICH und zwei hinter dem RICH. Die Superlagen bestehen aus drei Stereolagen. Jeweils zwei sind um  $\pm$  5° gegen die 0°-Lage (y-Richtung) verdreht. Der ITR<sup>4</sup> deckt den Winkelbereich von 10–100 mrad ab. Die Auflösung in x-Richtung beträgt  $\sigma_x = 100 \, \mu \text{m}$ , in y-Richtung  $\sigma_y = 1 \, \text{mm}$ .

#### Äußere Spurkammern (OTR)

Die äußeren Spurkammern [Cap 00] sind aus Driftkammern mit Bienenwabenstruktur aufgebaut. Damit die Detektorbelegungsdichte pro Kanal 20 % nicht überschreitet, besitzen die Driftkammern im inneren Bereich einen Durchmesser von 5 mm und im äußeren Bereich einen Durchmesser von 10 mm. Der OTR<sup>5</sup> besteht aus 7 Superlagen, jede Superlage wiederum aus drei Stereolagen. Analog zum ITR sind zwei Lagen um  $\pm$  5° gegen die 0°-Lage (y-Richtung) verdreht, um eine bessere räumliche Auflösung zu erhalten. Eine Superlage befindet sich vor dem Magneten, vier zwischen Magnet und RICH und zwei zwischen RICH und ECAL. Der OTR deckt den Winkelbereich von  $100-250\,\mathrm{mrad}$  ab. Die Auflösung beträgt  $\sigma=350\,\mu\mathrm{m}$ .

<sup>&</sup>lt;sup>4</sup>engl. Inner Tracker

<sup>&</sup>lt;sup>5</sup>engl. Outer Tracker

#### Spurkammern für Teilchen mit hohem Transversalimpuls (High- $P_T$ )

Im Magnetfeld befinden sich drei Lagen des so genannten High- $P_T$ -Spurkammersystems [HERA-B 00b] (High Pt). Es soll steife Spuren mit hohem Transversalimpuls identifizieren und die Informationen an das Triggersystem weiterleiten. Im inneren Bereich werden Gas-Pixel-Kammern verwendet, im äußeren Bereich besteht das Spurkammersystem aus zylinderförmigen Driftkammern mit Kathodenflächen (Kathoden-Pads).

#### 2.2.2 Detektoren zur Teilchenidentifikation

Zur Teilchenidentifikation werden der RICH-Detektor, der Übergangsstrahlungsdetektor, das Myon-System und das elektromagnetische Kalorimeter eingesetzt. Die aufgelisteten Subdetektoren werden in den folgenden Abschnitten erläutert.

#### Der Übergangsstrahlungsdetektor (TRD)

Die Aufgabe des Übergangsstrahlungsdetektors (TRD<sup>6</sup>) [Har 95] ist die Separation von Elektronen und Hadronen, im Wesentlichen Pionen. Der Übergangsstrahlungsdetektor besteht aus 32 Proportionalzählrohren, zwischen denen sich die Radiatorfolien befinden. Die Gesamtenergie der Strahlung ist abhängig vom Lorentzfaktor, weshalb Elektronen im Mittel höhere Übergangsstrahlung beim Durchgang durch den Grenzbereich zweier Materialien erzeugen als Hadronen. Daher lassen sich Hadronen und Elektronen gut separieren.

#### Das elektromagnetische Kalorimeter (ECAL)

Die Aufgabe des ECAL [Avo 01] ist es, Elektronen und Positronen zu identifizieren und ihre Energie zu messen. Zusätzlich wird die Energie von Photonen im Bereich von  $5-200\,\mathrm{GeV}$  gemessen. Ein weiterer wichtiger Punkt ist die Bereitstellung von Pretrigger-Signalen. Das ECAL ist ein Sampling-Kalorimeter, dessen Granularität vom inneren zum äußeren Bereich im Verhältnis 25:4:1 abnimmt. Da in allen drei Bereichen des ECAL der Molière-Radius kleiner als die halbe Kantenlänge einer Kalorimeterzelle sein soll, besteht das Konvertermaterial im inneren Bereich aus eine W-Ni-Fe-Legierung, während es im mittleren und äußeren Bereich aus Blei besteht. Die Tiefe des ECAL entspricht ca. 20 Strahlungslängen. Die Energieauflösung im inneren Bereich beträgt  $\sigma(E)/E = \frac{22,5\%}{\sqrt{E}} \pm 1,7\%$ . Im äußeren und mittleren Bereich liegt sie bei  $\sigma(E)/E = \frac{10\%}{\sqrt{E}} \pm 1,0\%$  [Zoc 00]. Der innere Bereich des ECAL liefert die Eingangsdaten für das ECAL-Energie-Veto-System (EEI<sup>7</sup>).

#### Der Myondetektor

Der Myondetektor [Tit 00] dient zur Identifizierung von Myonen und der Bereitstellung von Pretrigger-Signalen für das Triggersystem. Er besteht aus vier Superlagen und drei Absorberblöcken, die sich jeweils vor der ersten, zweiten und dritten Superlage

<sup>&</sup>lt;sup>6</sup>engl. Transition Radiation Detector

<sup>&</sup>lt;sup>7</sup>ECAL Energy Inhibit

befinden. Die erste und zweite Superlage bestehen im inneren Bereich aus Draht-Pixel-Kammern, im äußeren Bereich aus Proportionalkammern. Die Draht-Pixel-Kammern sind aus quadratischen Zellen, in denen parallel zum Strahl Anoden- und Kathodendrähte gespannt sind, aufgebaut. Im äußeren Bereich sind die Superlagen aus drei Stereolagen aufgebaut, die um  $\pm$  20° gegen die 0°-Lage (y-Richtung) verdreht sind. Die Superlagen drei und vier besitzen im inneren Bereich ebenfalls Draht-Pixel-Kammern, der äußere Bereich besteht jedoch nur aus einer Proportionalkammerlage, der 0°-Lage, in der sich zusätzlich Kathodenauslesepads befinden. Die Trefferinformation der Kathodenpads wird unter anderem vom Myon-Pretrigger zur Erzeugung der Pretrigger-Nachrichten ausgewertet.

#### Der RICH-Detektor

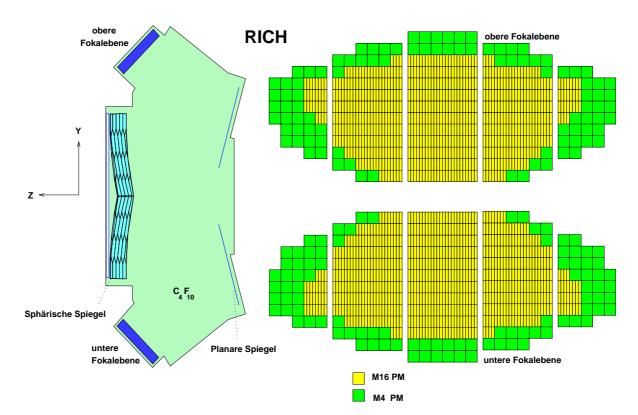

Die Aufgabe des ringabbildenden Cherenkov-Hodoskops [Pyr 00] (RICH<sup>8</sup>) ist die Identifikation von Hadronen mit einem hohen Impuls. Ein geladenes Teilchen mit einer Geschwindigkeit v > c/n strahlt in einem Medium mit dem Brechungsindex n einen Lichtkegel mit dem Öffnungswinkel  $\cos \theta_c = \frac{1}{n\beta}$  ab, wobei  $\beta$  das Verhältnis der Teilchengeschwindigkeit zur Vakuumlichtgeschwindigkeit ist. Bei bekanntem Impuls kann aus dem Winkel  $\theta_c$  die Geschwindigkeit und somit die Masse des Teilchens berechnet werden. Neben der Trennung von Pionen, Kaonen und Protonen kann der RICH auch als Spurdetektor eingesetzt werden [Duj 99], da aus dem Mittelpunkt und dem Radius der Ringe auf die Steigung der Spur geschlossen werden kann. Der RICH liefert die Eingangsdaten für das RICH-Multiplizitätsveto-System.

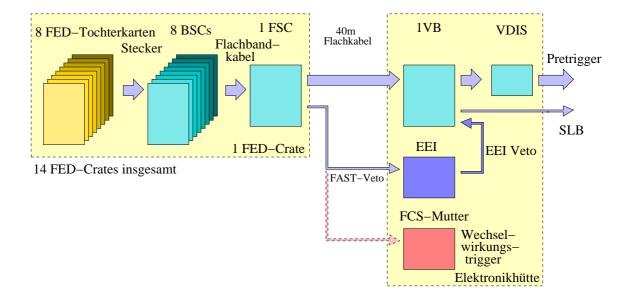

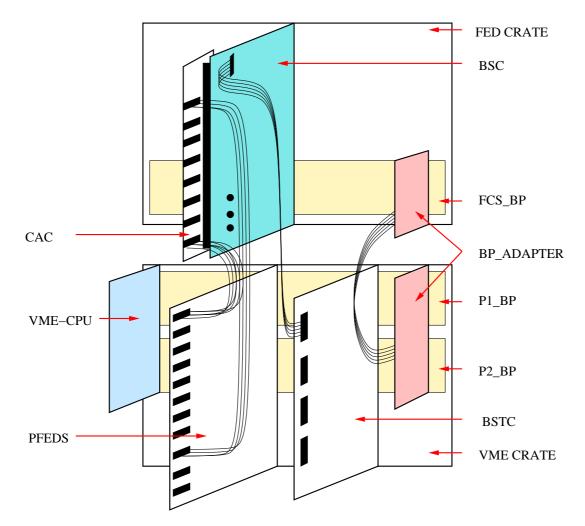

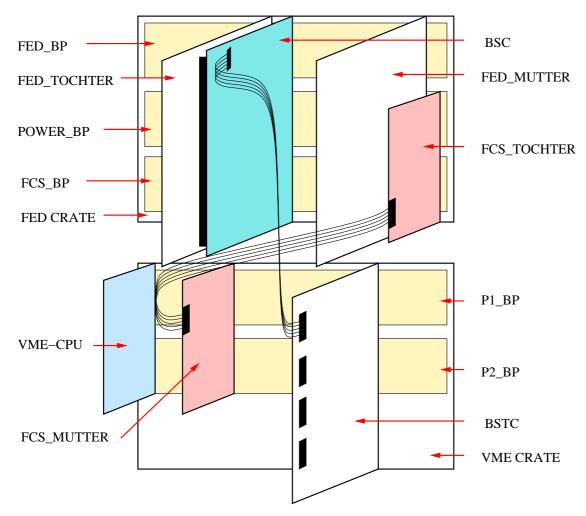

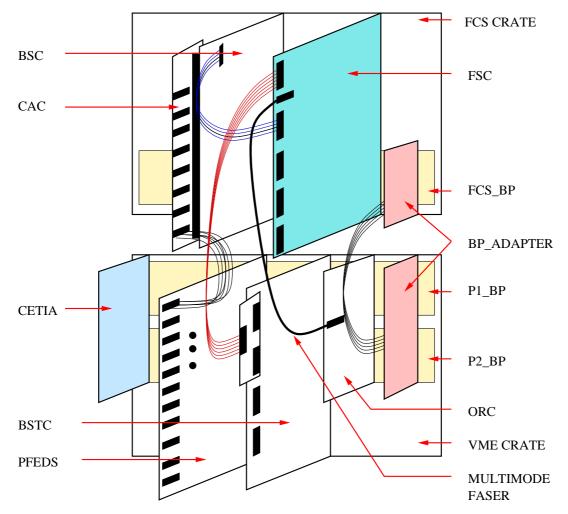

Der RICH-Tank ist aus Stahl gefertigt. Er besitzt Aluminiumfenster zum Ein- und Austritt des Protonstrahls. Das Licht verlässt den Tank über 2 mm dicke Plexiglasfenster. Der Tank ist mit 100 m<sup>3</sup> C<sub>4</sub>F<sub>10</sub>-Gas gefüllt, das eine Dispersion kleiner 5 % in dem benutzten Wellenlängenbereich von 300-480 nm besitzt. Das Licht wird über sphärische und planare Spiegel auf zwei Fokalebenen abgebildet, die den Detektor horizontal teilen. Eine schematische Darstellung des RICH-Tanks und der Fokalebenen ist in Abblidung 2.3 gezeigt. Die Photonen werden über unterschiedlich segmentierte Multi-Anoden-Photomultiplier<sup>9</sup> (PM) nachgewiesen und in elektrische Signale umgewandelt. Die PMs im inneren Bereich besitzen 16 Anoden (M16), die im äußeren Bereich vier Anoden (M4). Die Signale der PMs werden der Front-End-Elektronik (FEE) zugeführt, die eine Verstärkung und Pulsformung durchführt. Von der FEE werden die Daten über Flachkabel<sup>10</sup> an das Front-End-Treiber-System (FED<sup>11</sup>-System) übertragen. Das RICH-FED-System ist modular aufgebaut und befindet sich in direkter Nähe zum RICH-Detektor. In den FED-Crates<sup>12</sup> sind jeweils zwei FED-Mutterkarten und bis zu acht FED-Tochterkarten untergebracht. Auf den FED-Tochterkarten werden die Daten der FEE verarbeitet und im FED-Speicher zwischengespeichert. Der FED-Speicher ist ringartig aufgebaut und besitzt 128 Speicherplätze. Die Speicherplätze werden alle 128 BX mit neuen Daten überschrieben. Die Daten der von der ersten Triggerstufe

<sup>&</sup>lt;sup>8</sup>Ring Imaging Cherenkov Hodoscope

<sup>&</sup>lt;sup>9</sup>engl. für Sekundärelektronen-Vervielfacher

<sup>&</sup>lt;sup>10</sup>Als Flachkabel werden im Folgenden Flachbandkabel mit paarweise verdrillten Adern bezeichnet.

<sup>&</sup>lt;sup>11</sup>engl. Front End Driver

<sup>&</sup>lt;sup>12</sup>Ein Crate ist ein Einschubrahmen für Leiterplatten.

Abb. 2.3: Schematische Darstellung des RICH-Tanks und der Fokalebenen. In der Darstellung der Fokalebenen sind die verwendeten M16- bzw. M4-Photomultiplier-Module (PM) farblich unterschiedlich unterlegt. Die M16-Photomultiplier sind zusätzlich feiner gerastert eingezeichnet (nach [Pyr 00]).

akzeptierten Ereignisse werden aus den FED-Speichern ausgelesen und der zweiten Triggerstufe zur Verfügung gestellt.

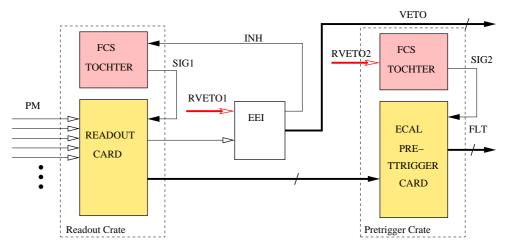

Im RICH werden 1543 M16- und 762 M4-Photomultiplier eingesetzt. Daraus resultieren 27736 Auslesekanäle, die von dem FED-System alle 96 ns verarbeitet werden müssen. Die FED-Tochterkarten besitzen jeweils 256 Kanäle. Es werden 14 FED-Crates, bestückt mit bis zu acht FED-Tochterkarten, zur Bearbeitung aller anfallenden Daten benötigt.

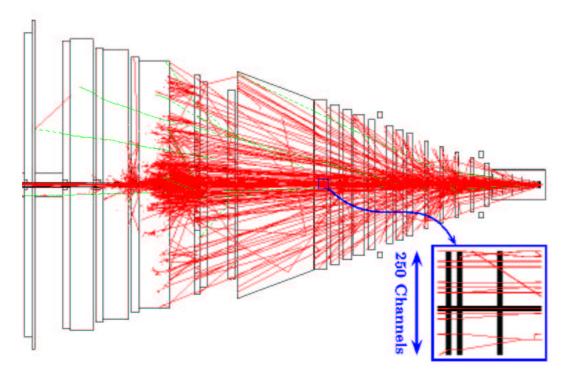

#### 2.3 Das Triggersystem

Der HERA-B Detektor erzeugt alle 96 ns 500 kByte Daten [Lüd 96], was einer Datenrate von ca. 5 TByte/s entspricht. Da es technisch nicht möglich ist, den gesamten Datensatz dauerhaft zu speichern, muss die Selektion der physikalisch interessierenden Ereignisse bereits während der Datenauslese, also vor der Rekonstruktion und Endspeicherung, geschehen. In Abbildung 2.4 ist ein typisches Ereignis im HERA-B Detektor dargestellt. Pro Ereignis mit im Mittel 4,6 überlagerten Wechselwirkungen werden ca. 200 Teilchenspuren geladener Teilchen erzeugt. Aus diesen müssen die physikalisch relevanten herausgefiltert werden, um zu bestimmen, ob die Daten des Ereignisses gespeichert oder verworfen werden sollen.

Abb. 2.4: Visualisierung eines Ereignisses im HERA-B Detektor bei im Mittel 4,6 überlagerten Wechselwirkungen. Es sind die erzeugten Spuren eines Ereignisses und die Detektorkomponenten schematisch dargestellt. [Loh 94]

Das HERA – B Experiment wurde entwickelt, um die CP-Verletzung im System der B-Mesonen zu untersuchen, wobei der Zerfall B  $\to$  J/ $\psi$ K $_{\rm S}^0$  der wichtigste Zerfallskanal ist. Die Triggerstrategie des HERA – B Experiments zielt darauf, J/ $\psi$ s schon in der ersten Triggerstufe zu finden. Dazu werden die zwei Leptonen aus dem J/ $\psi$ -Zerfall nachgewiesen, die entgegengesetzte Ladung haben und deren Energie der Masse eines J/ $\psi$ s entspricht. Die erste Triggerstufe (FLT $^{13}$ ) bestimmt die Spurparameter durch Messung der Impulse und Ladungen und berechnet die invariante Masse der Leptonenpaare. Sind Spuren rekonstruiert, ihre kinematischen Parameter und die invarianten Massen der Spurpaare bestimmt, wird die Triggerentscheidung an das Fast Control System (FCS) weitergeleitet, das die Auslese der Daten aus den FED-Speichern der einzelnen Subsysteme initialisiert. Die Daten werden im Second-Level-Buffer $^{14}$  zwischengespeichert.

Die zweite Triggerstufe (SLT<sup>15</sup>) verfeinert die Spursuche unter Zuhilfenahme zusätzlicher Detektorinformationen. Sie projiziert die Spuren durch den Magneten und führt einen Vertexfit durch. Die dritte Triggerstufe (TLT<sup>16</sup>) analysiert die Ereignisse, bei denen die in den vorangegangenen Stufen gefundenen Spuren nicht von einem gemeinsamen Vertex stammen. Dies trifft z. B. für semileptonische und hadronische Zerfälle

<sup>&</sup>lt;sup>13</sup>engl. First Level Trigger

<sup>&</sup>lt;sup>14</sup>engl. für Speicher der zweiten Stufe

<sup>&</sup>lt;sup>15</sup>engl. Second Level Trigger

<sup>&</sup>lt;sup>16</sup>engl. Third Level Trigger

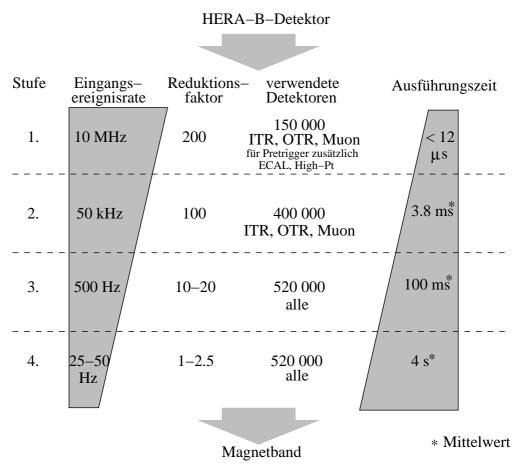

des B-Mesons zu. Die dritte Triggerstufe ist nicht mehr auf bestimmte Detektorgebiete begrenzt. Sie kann sämtliche Detektorinformationen zur Entscheidungsfindung heranziehen. Die vierte Triggerstufe (4LT<sup>17</sup>) führt eine komplette Rekonstruktion der Ereignisse unter Zuhilfenahme aller Detektordaten durch, fällt eine Triggerentscheidung aufgrund von Schnitten auf physikalische Parameter und speichert die akzeptierten Ereignisse auf Massenspeichern. Abbildung 2.5 zeigt die vier aufeinander folgenden Triggerstufen, ihre Eingangsereignisraten, Reduktionsfaktoren, verwendeten Detektoren und die Ausführungszeiten.

Abb. 2.5: Schematische Darstellung des vierstufigen Triggersystems (aus [Wag 00]). Die Eingangsereignisraten der einzelnen Triggerstufen, die Reduktionsfaktoren, die in den Triggerstufen verwendeten Detektoren und die Anzahl der Auslesekanäle sowie die Ausführungszeiten sind angegeben.

Aufgrund der Bedeutung für die vorliegende Arbeit werden die Pretrigger sowie die erste Triggerstufe und das Datennahmesystem detaillierter beschrieben.

<sup>&</sup>lt;sup>17</sup>engl. Fourth Level Trigger

#### 2.3.1 Die Pretrigger

Die erste Triggerstufe erhält von den Pretriggern zu jedem BX Informationen über mögliche Kandidaten für Myon-, Elektron- oder Hadronspuren, damit sie die Spurrekonstruktion aufnehmen kann. Die Pretrigger führen keine Untergrundunterdrückung durch, sondern liefern ausschließlich Startpunkte für die Spurrekonstruktion. Sie werden daher auch als nullte Triggerstufe bezeichnet. Um auf die oben genannten Signaturen sensitiv zu sein, existieren drei Pretrigger im HERA-B Experiment: der Myon-, der ECAL- und der High- $P_T$ -Pretrigger. Die Pretrigger-Systeme werden in den folgenden Abschnitten etwas ausführlicher beschrieben.

#### Der ECAL-Pretrigger und das ECAL Energy Inhibit (EEI)

Der ECAL-Pretrigger und das ECAL Energy Inhibit (EEI) sind technisch eng miteinander verbunden. Sie werden daher in diesem Abschnitt zusammen behandelt.

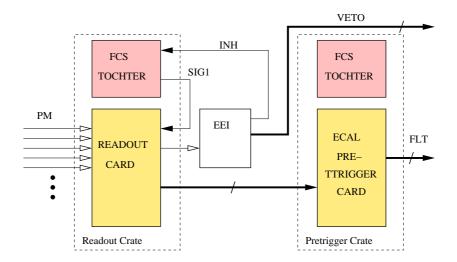

Zur Identifikation der Elektronen wird im ECAL-Pretrigger die deponierte Energie in Clustern von  $3\times3$  Kalorimeterzellen überprüft. Übersteigt die Energie eines Clusters einen einstellbaren Schwellwert  $E_{th}$  oder ist die Energie in der zentralen Zelle größer als der halbe Schwellenwert  $E_{th}$ , wird eine Nachricht für die erste Triggerstufe erzeugt. Zusätzlich wird eine Bremsstrahlungskorrektur durchgeführt. Das System besteht aus den Readout Cards, die die analogen Signale der Photomultiplier digitalisieren und die Daten an die Pretrigger Boards weiterleiten. Die Pretrigger Boards führen die Cluster-Suche durch und erzeugen die Nachrichten für die erste Triggerstufe. Das System besteht aus ca. 130 Readout Cards und ebensovielen Pretrigger Cards [HERA-B 00b].

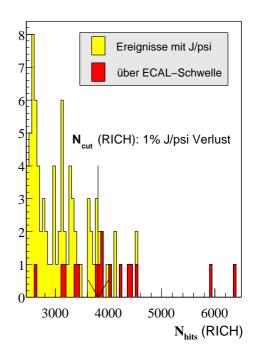

Das ECAL Energy Inhibit [Avo 02] verwendet zur Erzeugung des Veto-Signals die Informationen des inneren Kalorimeterbereichs. Es bildet die analoge Summe der deponierten Energien und vergleicht diese mit einer einstellbaren Schwelle. Überschreitet die Energiesumme die Schwelle, wird ein Veto-Signal erzeugt. Dieses wird mit der BX-Nummer des jeweiligen Ereignisses markiert und an den High- $P_T$ - und den Myon-Pretrigger weitergeleitet. Im ECAL-Pretrigger wird das Veto-Signal über die Fast-Control-System-Tochterkarten an die Readout Cards verteilt und unterdrückt die Datenverarbeitung auf den Pretrigger Boards. In Abbildung 2.6 ist der Aufbau des ECALs und des EEI schematisch dargestellt.

#### Der High-P<sub>T</sub>-Pretrigger

Der High- $P_T$ -Pretrigger [Bal 00] liefert Startpunkte für die Spurrekonstruktion von Teilchen mit hohem Transversalimpuls. Er nutzt dazu die Informationen der High- $P_T$ -Kammern innerhalb des Magneten. Die Kathoden-Pads der einzelnen Lagen sind projektiv angeordnet. Mit jedem Pad der ersten Ebene werden jeweils fünf Pads der zweiten bzw. sechs Pads der dritten Ebene verknüpft [Rie01]. Eine Trefferkoinzidenz in den verknüpften Pads definiert einen Startpunkt.

Das High-P<sub>T</sub>-Pretrigger-System ist modular aufgebaut. Es besteht im Wesentlichen aus drei Komponenten, den Link Boards (LB), den Pretrigger Boards (PTB) und den Message Generatoren (MG). Das gesamte Pretrigger-System umfaßt ca. 80 LBs, 40 PTBs

Abb. 2.6: Schematische Darstellung des ECAL-Pretriggers und des EEI. Dünn gedruckte offene Pfeile symbolisieren analoge Daten, dünn gedruckte geschlossene Pfeile Steuersignale und fett gedruckte Pfeile stehen für digitale Daten. Die analogen Daten der Photomultiplier (PM) gelangen auf die READOUT CARDs, auf denen sie digitalisiert und an die ECAL PRETRIGGER CARDs weitergeleitet werden. Dort wird die Cluster-Suche durchgeführt und die Nachricht für die erste Triggerstufe (FLT) generiert. Das EEI erhält analoge Daten, summiert diese analog und vergleicht sie mit einer einstellbaren Schwelle. Ist die Energiesumme größer als der Schwellenwert, wird ein Veto-Signal (VETO) erzeugt. Intern gelangt das Veto-Signal (INH) an die Fast-Control-System-Tochterkarten (FCS TOCHTER) der Readout Crates. Das Veto-Signal (SIG1) wird an die Readout Cards verteilt und unterbindet die Datenverarbeitung auf den ECAL PRETRIGGER CARDS.

und 8 MGs. Die Link Boards befinden sich in den High- $P_T$ -FED-Crates, in direkter Nähe des Detektors. Es existieren zwei Versionen der LBs, die dem Datenformat des Detektors angepasst sind. Das Pretrigger Board sucht nach Koinzidenzmustern in den Padinformationen der drei Detektorlagen. Gefundene Koinzidenzen werden an den Message Generator weitergeleitet, der eine Nachricht für die erste Triggerstufe generiert. Bei der Entwicklung des High- $P_T$ -Pretrigger-Systems wurde vorgesehen, dass die Datenverarbeitung über ein externes Veto-Signal unterdrückt werden kann. Über die Message Generatoren gelangt das Veto-Signal an die Pretrigger Boards. Die Daten des Pretrigger Boards werden in einer pipelineartig aufgebauten Speicherstufe zwischengespeichert, um sie mit dem Veto-Signal zu synchronisieren, falls die Latenzzeit des Pretriggers kürzer ist, als die der Veto-Signal-Erzeugung.

#### Myon-Pretrigger

Der Myon-Pretrigger [Böc 01] benutzt zur Suche nach Startpunkten Informationen der letzten beiden Superlagen des Myondetektors. Diese Superlagen sind aus Propor-

tionalkammern aufgebaut und besitzen eine zusätzliche Kathoden-Pad-Auslese. Der Pretrigger sucht nach Trefferkoinzidenzen der Pads in den unterschiedlichen Lagen. Dabei werden im äußeren Bereich die Pads der dritten Superlage jeweils mit sechs Pads der vierten Superlage, die in Projektion der Teilchenbahn liegen, verknüpft. Im inneren Bereich werden sogenannte Pseudopads aus den Pixelzellen gebildet. Aufgrund der höheren Granularität wird hier jeweils ein Pseudopad der dritten Superlage mit vier Pseudopads der vierten Superlage verknüpft.

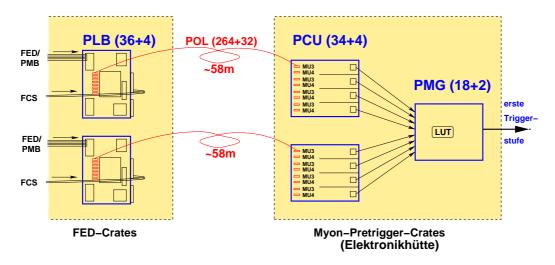

Abb. 2.7: Schematische Darstellung des Myon-Pretriggers. Die PLBs übertragen die Daten des Detektors mittels des POLs zu den PCUs in die Elektronikhütte. Die PCUs berechnen die Koinzidenzen, aus denen der PMG Nachrichten für die erste Triggerstufe erzeugt.

Der Myon-Pretrigger besteht aus vier Hauptkomponenten, wie in Abbildung 2.7 zu erkennen. Die Pretrigger Link Boards (PLB) erhalten die Daten vom Myon-FED-System. Das FED-System befindet sich in direkter Nähe des Detektors. Die Daten werden mit den Pretrigger Optical Links (POL) über ca. 50 m in die Elektronikhütte zur Pretrigger Coincidence Unit (PCU) übertragen. Die PCU berechnet die Koinzidenzen und gibt diese an den Pretrigger Message Generator (PMG) weiter. Dieser erzeugt eine Nachricht für die erste Triggerstufe. Das Myon-Pretriggersystem umfaßt 40 PLBs, 38 PCUs und 20 PMGs.

Auch im Myon-Pretrigger wurde die Unterdrückung der Pretrigger-Nachrichten während der Entwicklung vorgesehen. Wie beim High- $P_T$ -Pretrigger gelangt das Veto-Signal über die PMGs auf die PCUs. Die Daten der asynchron zum HERA-Takt laufenden optischen Übertragungsstrecken werden zur Synchronisation unter der mit den Daten mitgelieferten BX-Nummer in DPRAMs gespeichert. Auch das Veto-Signal wird unter der mitgelieferten BX-Nummer in einem DPRAM gespeichert. Die Daten und das Veto-Signal werden zu der aktuell auf der PCU verarbeiteten BX-Nummer ausgelesen. Ist das Veto-Signal gesetzt, werden keine Daten an die PMGs übertragen.

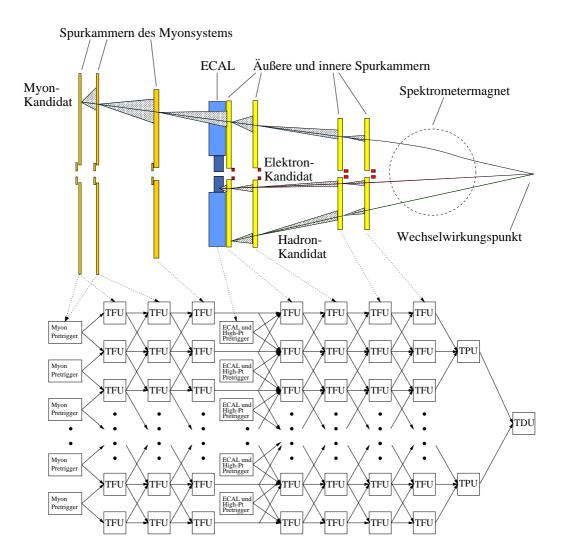

Abb. 2.8: Darstellung des matrixartigen Netzwerks des FLT und den zugehörigen Detektorlagen (aus [Nör 99]). Jeder TFU ist eine Suchregion einer Detektorlage zugeordnet. Auf der TPU werden die Parameter der Spuren berechnet und Schnitte auf den Transversalimpuls durchgeführt. Die Spurinformation wird an die TDU weitergeleitet, die die Triggerentscheidung fällt.

#### 2.3.2 Die erste Triggerstufe (FLT)

Wie bereits erwähnt, untersucht die erste Triggerstufe [Ful 98a] (FLT<sup>18</sup>) jedes Ereignis, rekonstruiert Teilchenspuren und führt Schnitte auf physikalische Parameter aus. Die Verarbeitung der damit verbundenen hohen Dateneingangsrate und die kurze Triggerentscheidungszeit von  $12,3\,\mu$ s inklusive der Latenzzeiten der Pretrigger sind die wesentlichen Herausforderungen der ersten Triggerstufe.

Die erste Triggerstufe ist aus speziell entwickelten Elektronikmodulen aufgebaut, die auf Hardware-Ebene einen Kalman-Filter-Algorithmus [Boc00] durchführen. Dabei wird,

<sup>&</sup>lt;sup>18</sup>engl. First Level Trigger

ausgehend von den Startpunkten der Pretrigger, die Spur entgegen der Flugrichtung der Teilchen durch die Detektorlagen verfolgt. In Abbildung 2.8 sind die von der ersten Triggerstufe benutzten Detektorkomponenten und das matrixförmig aufgebaute Netzwerk der Elektronikmodule dargestellt. Jeder Track Finding Unit (TFU) ist ein Detektorbereich einer Detektorlage zugeordnet. Über optische Übertragungsstrecken gelangen die Daten der Detektorlagen von den FEDs auf die TFUs. Dort werden die Daten der letzten 128 BX in Wire Memories (eigens zu diesem Zweck entwickelten ASICs<sup>19</sup>) zwischengespeichert, um den Datentransfer zu reduzieren. Die TFUs erhalten von den TFUs der vorherigen Lage oder den Pretriggern die Information, in welcher Suchregion (Region of Interest) nach Treffern gesucht werden soll. Die Suchregion für die nachfolgende TFU-Lage wird berechnet und an die entsprechenden TFUs weitergeleitet. Die Daten der letzten TFU-Lage werden an die Track Parameter Units (TPU) übertragen. Diese berechnen die zugehörigen Spurparameter und führen Schnitte auf den Transversalimpuls durch. Alle akzeptierten Spuren werden in der Trigger Decision Unit (TDU) gesammelt. Es werden die Spuren der Elektronen und Myonen gezählt und die invariante Masse für Spurpaare berechnet. Es existieren zwei Trigger-Modi. Bei dem Zähltrigger-Modus wird auf die Anzahl einer bestimmten Teilchensorte getriggert, während im Paartrigger-Modus auf die invariante Masse des J/ $\psi$ s getriggert wird. Die Spurinformationen und Suchregionen der akzeptierten Ereignisse werden an die zweite Triggerstufe weitergegeben.

#### 2.3.3 Das Datennahmesystem

Die Detektordaten der einzelnen Subdetektoren sind in den FED-Speichern der jeweiligen subdetektorspezifischen FEDs für 128 BX gespeichert. Werden Ereignisse akzeptiert, ist es die Aufgabe des Datennahmesystems, die zugehörigen Daten aus den FED-Speichern auszulesen und an die zweite Triggerstufe weiterzuleiten. Dies wird durch das Fast Control System (FCS) koordiniert. Das FCS verteilt ein Taktsignal und die BX-Nummer an die FEDs des gesamten HERA-B Experiments. Unter der Adresse der BX-Nummer werden die Detektordaten in den FED-Speichern zwischengespeichert. Die Adresse unter der die akzeptierten Ereignisse ausgelesen werden, wird vom FCS an die FED-Speicher weitergeleitet. Die Leseadresse wird im Folgenden als FLT-BX-Nummer bezeichnet. Eine detailliertere Beschreibung des FCS wird in Abschnitt 9.2 gegeben.

Die Informationen aus den FED-Speichern werden an den Second-Level-Buffer übertragen. Dieser ist aus einem Netzwerk miteinander kommunizierender  $\mathrm{DSPs^{20}}$  aufgebaut. Die Weiterverteilung der Daten in den höheren Triggerstufen wird von dem sogenannten Event-Controller gesteuert.

<sup>&</sup>lt;sup>19</sup>Application Specific Integrated Circuit

<sup>&</sup>lt;sup>20</sup>Digital Signal Prozessor engl. für digitaler Signal-Prozessor

### Kapitel 3

### Das Physikprogramm von HERA-B

Wie im vorhergehenden Kapitel bereits geschilder, wurde das HERA-B Experiment zum Nachweis der CP-Verletzung im System der neutralen B-Mesonen entwickelt. Es besitzt eine gute Vertexauflösung und Teilchenidentifikation. Ein Großteil der pro Ereignis auftretenden Teilchenspuren kann rekonstruiert werden. Die kinematische Akzeptanz des Detektors erstreckt sich über den Bereich  $-0.4 < x_F < 0.3$  und eröffnet damit den Zugang zu Messungen bei negativen  $x_F$ -Werten. Dieser Bereich wird von anderen Experimenten mit festem Target typischerweise nicht abgedeckt.

Die Fertigstellung des HERA-B Detektors verzögerte sich gegenüber dem ursprünglichen Zeitplan. Die hohen Teilchenflüsse stellten besondere technische Anforderungen an den Bau und die Inbetriebnahme der Spurdetektoren und des Triggersystems und führten zu unvorhergesehenen Problemen. Die Verzögerung bei der Inbetriebnahme des HERA-B Detektors und die schnellere und erfolgreichere Inbetriebnahme der auf dem Gebiet der B-Meson-Physik konkurrierenden Experimente an den e<sup>+</sup>e<sup>-</sup>-Speicherringen führten dazu, die Prioritäten des Physikprogramms für die Datennahmeperiode 2002 neu zu definieren [HERA-B 00b, HERA-B 00a, HERA-B 01]. Da HERA-B Hadron-Streuprozesse untersucht, liegt es nahe, Forschungen im Bereich der Quantenchromodynamik (QCD) zu betreiben. Mit den Untersuchungen können die Vorhersagen der QCD getestet und ungeklärte Aspekte untersucht werden.

Das Physikprogramm der Datennahmeperiode 2002/2003 wird sich auf die Messung des bb-Wirkungsquerschnitts und der Charmonium-Unterdrückung als Funktion der nuklearen Target-Masse A konzentrieren. Diese beiden Themen werden in den folgenden Abschnitten kurz skizziert. Die theoretischen Modelle werden vorgestellt und der mögliche Beitrag des HERA-B Experiments zu diesen Themen aufgezeigt.

# 3.1 Harte Parton-Streuung, Renormierung und Faktorisierung

Im Quark-Parton-Modell wird der Wirkungsquerschnitt  $\sigma(S, m^2)$  einer Hadron-Hadron-Wechselwirkung durch die Parton-Dichten  $F_i$ ,  $F_j$  und den partonischen Wirkungsquerschnitt  $\sigma_{ij}$  wie folgt beschrieben:

$$\sigma(S, m^2) = \int dx_1 dx_2 \sum_{ij} F_i(x_1, \mu^2) F_j(x_2, \mu^2) \, \sigma_{ij}(s, m^2, \mu^2).$$

Die Parton-Dichten  $F_i(x, \mu^2)$  können nicht perturbativ berechnet werden. Die Indizes i, j stehen für ein Quark, Antiquark oder Gluon. Mit der Variablen Bjorken-x,  $x_{1,2}$ , wird der Bruchteil des Hadronimpulses angegeben, der von dem wechselwirkenden Parton getragen wird. S ist das Quadrat der Schwerpunktsenergie und s ist definiert als  $s = x_1 x_2 S$ . Die Masse des produzierten schweren Quarks ist m. Die Wahl der Renormierungskonstante  $\mu$  hängt von der Renormierungsskala ab. Bei der Entwicklung des partonischen Wirkungsquerschnitts in Potenzreihen der Kopplungskonstanten der QCD,  $\alpha_s$ , treten zwei Typen von Divergenzen auf: die Infrarotdivergenz und die Ultraviolettdivergenz. Die Ultraviolettdivergenz wird durch Schleifendiagramme hervorgerufen, in denen der Partonimpuls nicht eingeschränkt ist. Diese Divergenzen werden durch sogenannte Renormierungsprozeduren beseitigt. Dadurch wird eine Skala  $\mu_R$  eingeführt, bei der die Subtraktion, durch die die Divergenzen aufgehoben werden, stattfindet. Die Kopplungskonstante  $\alpha_s$  wird durch die renormierte Kopplungskonstante  $\alpha_s(\mu_R)$  ersetzt. Die langreichweitige (weiche) und kurzreichweitige (harte) Dynamik des Streuprozesses wird in der QCD in universelle, nicht-perturbative Partonverteilungs- und Fragmentierungsfunktionen, und störungstheoretisch berechenbare Streufunktionen unterteilt. Die Infrarotdivergenzen, bei denen der Partonimpuls gegen null geht, werden in den nicht-perturbativen Anteil des Wirkungsquerschnitts faktorisiert. Das Faktorisierungs-Theorem [Col 88] erlaubt die Separation des weichen Anteils von dem harten. Die Separation wird durch die Faktorisierungsskala  $\mu_F$  festgelegt. Die Parameter  $\mu_R$  und  $\mu_F$  sind willkürliche Parameter. Sie werden jedoch meistens so gewählt, dass sie in der Größenordnung des Impulsübertrages Q bei der harten Wechselwirkung liegen:

$$\mu_R = \mu_F = \mu = Q.$$

# 3.2 Bestimmung des Wirkungsquerschnitts $\sigma_{b\overline{b}}$ nahe der Produktionsschwelle

Die Berechnung des Produktionswirkungsquerschnitts schwerer Quarks in der QCD wird mittels des Faktorisierungs-Theorems und der Entwicklung der beitragenden Amplituden in Potenzen der Kopplungskonstante  $\alpha_s$  durchgeführt. Dabei wird ein Teil der Strahlungskorrekturen, die aufgrund der Abstrahlung weicher Gluonen eingeführt werden müssen, in den Strukturfunktionen zusammengefasst und ist damit abhängig vom Faktorisierungsschema. Bei der perturbativen Entwicklung können die logarithmischen Terme nahe der Produktionsschwelle große Werte annehmen, die resummiert werden müssen, um die theoretischen Vorhersagen zu präzisieren. Die Summation findet in allen Ordnungen Störungstheorie statt. Die Logarithmen sind vom Typ  $(\ln(1-z))^i/(1-z)$ , wobei i die Ordnung der perturbativen Entwicklung angibt. Bei diesen Ausdrücken muss über die Variable z bis zu einem Limit von z=1 integriert werden. Die Ausdrücke besitzen zwar keine Singularität bei z=1, da in dem Integranden Terme  $\delta(1-z)$  berücksichtigt werden müssen, können jedoch den Hauptbeitrag der Korrekturterme bilden [Kid 96]. Im folgenden Abschnitt werden die theoretischen Berechnungen für die Produktionswirkungsquerschnitte schwerer Quarks in führender (LO<sup>1</sup>)

$<sup>^{1}</sup>$ engl. leading order

und nächstführender Ordnung (NLO<sup>2</sup>) der perturbativen QCD kurz zusammengefasst. Dabei wird weitgehend der Notation aus [Nas 88] gefolgt.

Der totale Wirkungsquerschnitt  $\sigma$  wird durch folgende Faktorisierungsformel gegeben:

$$\sigma(\rho_h, m^2) = \sum_{i,j} \int_0^1 dx_1 dx_2 F_i(x_1, \mu^2) F_j(x_2, \mu^2) \sigma_{ij}(\rho, m^2, \mu^2),$$

wobei m die Masse des schweren Quarks und i, j die Indizes der Partonen angibt  $(i = g, q, \overline{q})$ .  $\rho$  und  $\rho_h$  sind dimensionslose Variablen

$$\rho_h = \frac{4m^2}{S}, \quad \rho = \frac{\rho_h}{x_1 x_2}.$$

S ist das Quadrat der Schwerpunktsenergie. Die Partondichten  $F_i(x, \mu^2)$  und der partonische Wirkungsquerschnitt  $\sigma_{ij}$  hängen von der Faktorisierungsskala  $\mu$  und dem Faktorisierungsschema ab. Es wird die dimensionslose Funktion  $f_{ij}$  eingeführt, indem der partonische Wirkungsquerschnitt folgendermaßen umgeschrieben wird:

$$\sigma_{ij}(\rho, m^2, \mu^2) \equiv \frac{\alpha_S^2(\mu^2)}{m^2} f_{ij}(\rho, \alpha_s(\mu^2), \mu^2/m^2).$$

Die Funktionen  $f_{ij}$  sind perturbativ berechenbar und werden durch folgende Entwicklung in  $\alpha_s$  bestimmt:

$$f_{ij}(\rho,\alpha_s(\mu^2),\frac{\mu^2}{m^2}) = f_{ij}^{(0)}(\rho) + 4\pi\alpha_s(\mu^2) \left[ f_{ij}^{(1)}(\rho) + \overline{f}_{ij}^{(1)}(\rho) \ln\frac{\mu^2}{m^2} \right] + \sum_{n=2}^{\infty} \alpha_s^n(\mu^2) f_{ij}^{(n)}(\rho,\frac{\mu^2}{m^2}).$$

Die  $\overline{f}_{ij}^{(1)}$ -Terme sind die Koeffizienten von  $\ln \frac{\mu^2}{m^2}$  und werden mittels Renormierungsgruppenargumenten aus den  $f_{ij}^{(0)}$  in führender Ordnung bestimmt:

$$\overline{f}_{ij}^{(1)}(\rho) = \frac{1}{8\pi^2} \left[ 4\pi b_0 f_{ij}^{(0)}(\rho) - \int_{\rho}^1 dz_1 f_{kj}^{(0)}(\frac{\rho}{z_1}) P_{ki}(z_1) - \int_{\rho}^1 dz_2 f_{ik}^{(0)}(\frac{\rho}{z_2}) P_{kj}(z_2) \right].$$

Dabei wird die explizite Form der Altarelli-Parisi-Splitting-Funktionen  $P_{ij}$  [Alt 82, Alt 77] benutzt. Der Koeffizient  $b_0$  wird aus der Renormierungsgruppe bestimmt. Die verbleibenden NLO-Beiträge  $f_{ij}^{(1)}$  sind analytisch nicht berechenbar. Eine analytische Parametrisierung numerischer Resultate ist in [Nas 88] gegeben. Nahe der Produktionsschwelle,  $\rho \to 1$ , verschwinden die Terme der führenden Ordnung aufgrund der Phasenraumunterdrückung [Fri 98]. Die Terme in nächstführender Ordnung verschwinden jedoch nicht und tragen hauptsächlich zu den NLO-Korrekturen bei [Nas 88]. Die Funktionen  $f_{ij}^{(n)}(\rho,\mu^2/m^2)$  verhalten sich wie:

$$f_{ij}^{(n)}(\rho,\mu^2/m^2) \sim f_{ij}^{(0)}(\rho) \ln^{2n}(1-\rho).$$

Die Resummation der Effekte, hervorgerufen durch Abstrahlung weicher Gluonen, in allen Ordnungen Störungstheorie hilft, die Genauigkeit der QCD-Vorhersagen zu verbessern. In der theoretischen Berechnung des Produktionswirkungsquerschnitts bis zur

<sup>&</sup>lt;sup>2</sup>engl. next-to-leading order

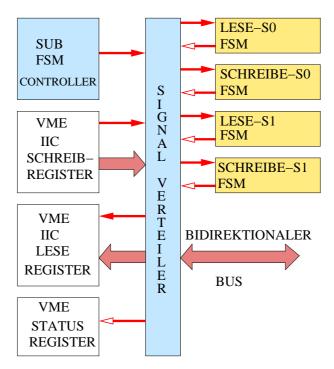

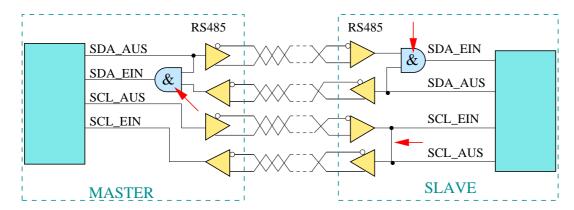

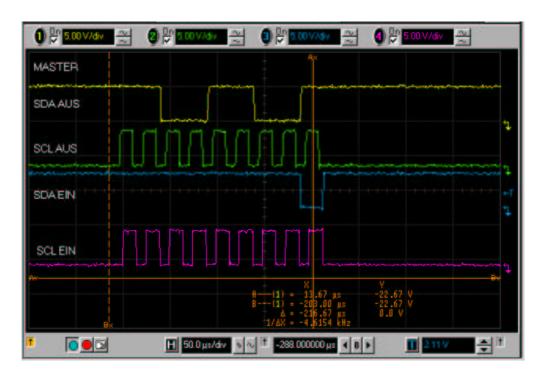

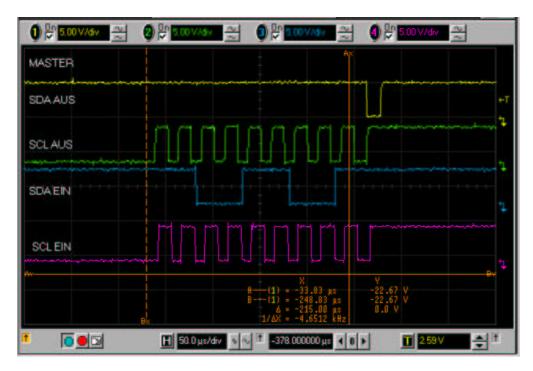

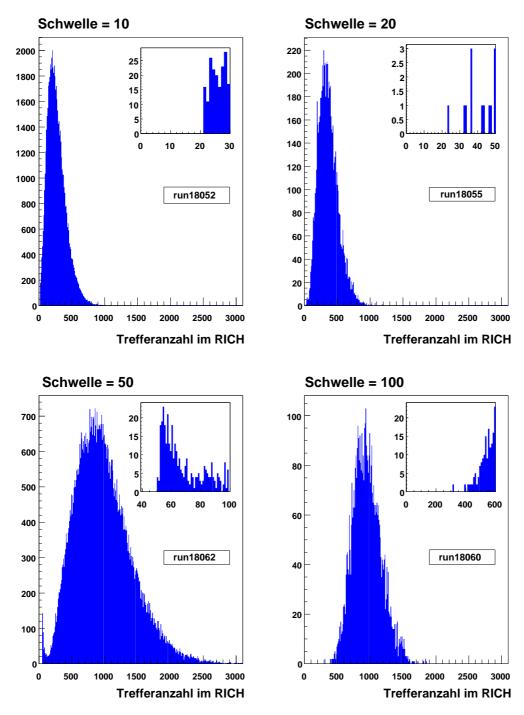

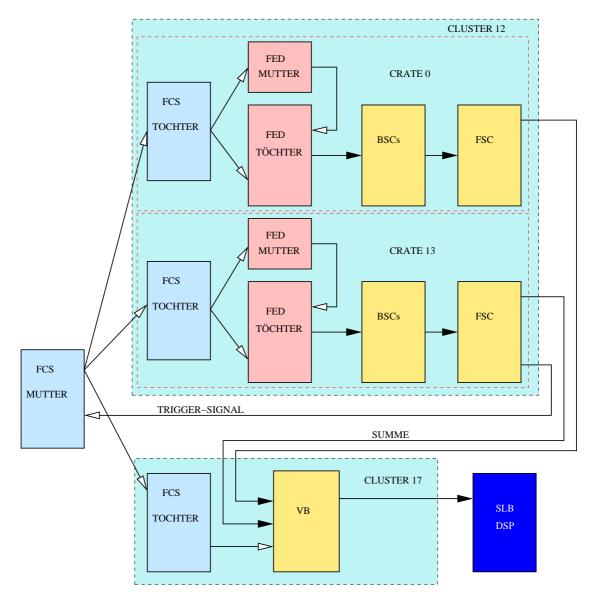

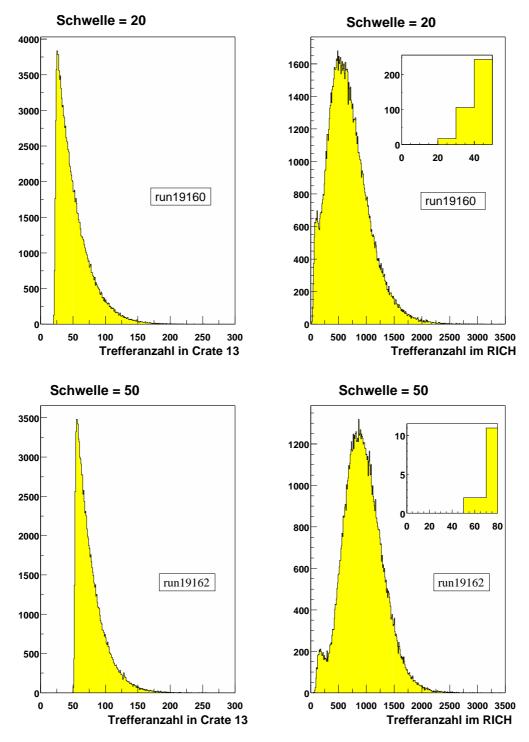

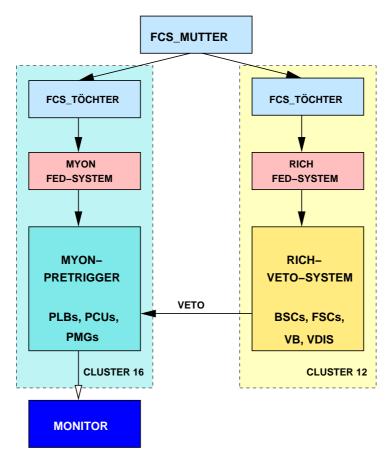

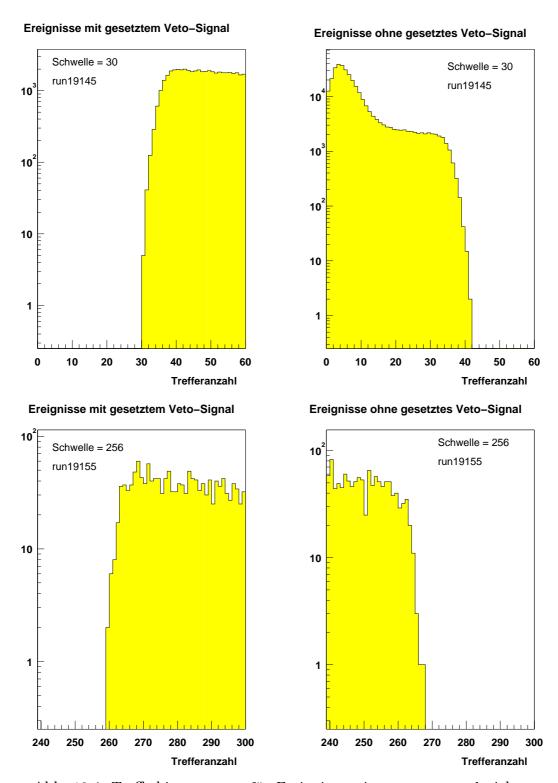

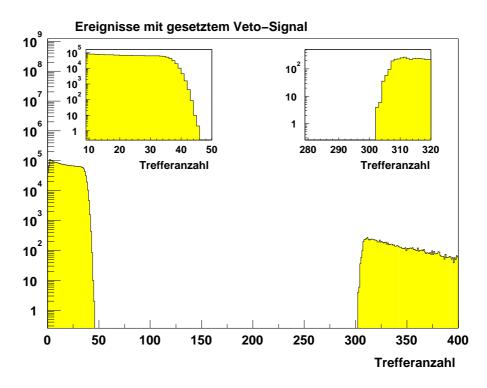

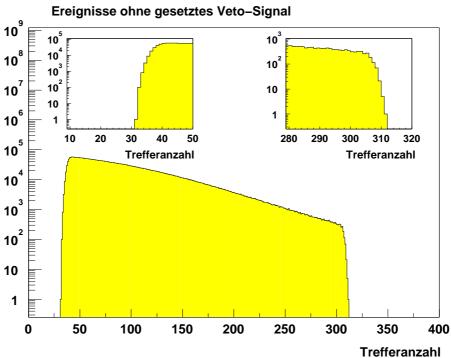

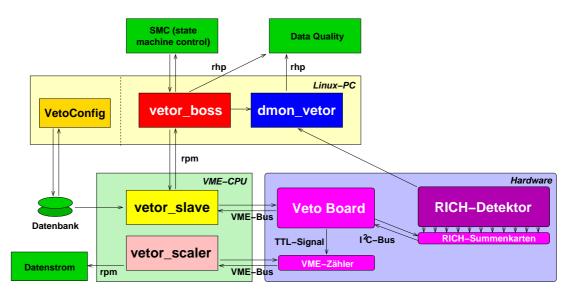

nächstführenden Ordnung hängt das Resultat stark von der Wahl des Skalenparameters  $\mu$  ab. Die Berücksichtigung von Termen höherer Ordnungen in der Störungsrechnung (NLL³) zeigen, dass die Skalenabhängigkeit des Produktionswirkungsquerschnitts deutlich reduziert wird [Bon 98, Kid 01].