# Fast and Accurate Finite-Element Multigrid Solvers for PDE Simulations on GPU Clusters

Dissertation

zur Erlangung des Grades eines

Doktors der Naturwissenschaften

Der Fakultät für Mathematik der Technischen Universität Dortmund vorgelegt von

Dominik Göddeke

Fast and Accurate Finite Element Multigrid Solvers for PDE Simulations on GPU Clusters Dominik Göddeke

Dissertation eingereicht am: 25. 2. 2010 Tag der mündlichen Prüfung: 10. 5. 2010

# Mitglieder der Prüfungskommission

Prof. Dr. Stefan Turek (1. Gutachter, Betreuer)

Prof. Dr. Heinrich Müller (2. Gutachter)

Prof. Dr. Joachim Stöckler Prof. Dr. Rudolf Scharlau

Dr. Matthias Möller

# Acknowledgements

It is impossible to acknowledge everyone who directly or indirectly contributed to the realisation of this thesis. I apologise to all those not mentioned by name: Your help and support is really appreciated.

In particular, I would like to express my sincere gratitude to the following people: Professors Stefan Turek and Heinrich Müller guided my scientific career from the first contact to Numerical Mathematics and Computer Graphics as an undergraduate student to the strongly interdisciplinary field of scientific computing in which I finally settled with this thesis. I am deeply indebted to them for giving me the opportunity to work in the friendly atmosphere at the Institute of Applied Mathematics and the Chair of Computer Graphics at TU Dortmund. I want to thank them for their ideas, fruitful discussions and encouraging criticisms, their belief in my work when I got lost, and last but not least for taking the risk and having the vision to support this endeavour into an emerging research area that at the beginning no one really expected to have such a big impact.

I am very grateful to my fellow PhD students and friends in the FEAST group, Christian Becker, Sven Buijssen, Matthias Grajewski and Hilmar Wobker. Developing such a large-scale package like FEAST is always a group effort, and I believe we did extremely well sharing the tedious task of implementing features for the common good even if it meant devoting the 'occasional' week for non-thesis work, while still pursuing our separate research projects. Knowing that I could always rely on our group for discussing design decisions, toying with ideas, going through painful debugging sessions, solving hardware, cluster and scheduling issues and related nightmares in parallel computing, and last but not least, sharing a beer if all else failed cannot be appreciated enough. The conference proceedings and journal papers we wrote together clearly do not tell the entire story. While not being technically members of the FEAST group, Matthias Möller, Thomas Rohkämper and Michael Köster are acknowledged for the same reasons.

I am very grateful to Robert Strzodka for our collaboration during the past years. What started out from his talk at my 'inauguration workshop' in early 2005 soon became a common vision that we pursued relentlessly. Without Robert, I would never have met Patrick McCormick and Jamaludin Mohd-Yusof from Los Alamos, and the research the four of us pursued together (and the papers we wrote) would not have been possible. In fact, Robert deserves the same credits for shaping me into a scientist as Stefan Turek and Heinrich Müller do.

Matthias Möller, Hilmar Wobker, Robert Strzodka and Jamaludin Mohd-Yusof deserve special credits for proofreading sections of this thesis and discussing questions that arose. Their constructive criticism helped a lot to improve clarity of this thesis and to make the presentation more concise.

In my time at TU Dortmund, I helped supervising quite a few Diploma theses and student project groups. Discussing ideas with 'my' students cannot be overestimated, and I believe this has always been fruitful for both sides. Among the works I supervised, I want to acknowledge Hendrik Becker, Markus Geveler, Dirk Ribbrock and Mirko Sykorra. One project group that I launched was so successful that we published the results in Computer Physics Communications, and I am

indebted to my co-authors Danny van Dyk, Markus Geveler, Sven Mallach, Dirk Ribbrock and Carsten Gutwenger for the opportunity to work together productively for more than two years.

NVIDIA and AMD/ATI supported my research through generous hardware donations, and I owe gratitude to Mark Harris, Mike Houston, David Luebke, Simon Green, Christian Sigg, Dominik Behr and Sumit Gupta for fruitful discussions and untiring assistance. The same is true for collaborators and colleagues I discussed many scientific and non-scientific ideas with at conferences or otherwise, in particular John Owens, Aaron Lefohn, Dimitri Komatitsch, Gordon Erlebacher, David Michéa, Cliff Woolley, Daniel Nogradi, Jonathan Cohen, Yao Zhang, Jens Krüger and Rüdiger Westermann; and virtually everyone I collaborated and exchanged ideas with in one form or another.

Finally, I am very grateful to my parents Michaela and Nikolaus, my sisters Maria and Anne and my brother Niklas for encouragement and support. My godchild Linda Lübbers, and Hannah, Jannis and Pia Imöhl made sure to keep me sane and focused through all these years.

Support of this work by the DFG (Deutsche Forschungsgemeinschaft) through the grants TU102/22-1 and TU102/22-2 is gratefully acknowledged.

Dortmund, February 25, 2010

Dominik Göddeke

# Contents

| 1 | Intr | oductio  | n                                                                     | 1  |  |

|---|------|----------|-----------------------------------------------------------------------|----|--|

|   | 1.1  | Introdu  | uction and Motivation                                                 | 1  |  |

|   |      | 1.1.1    | Hardware-Oriented Numerics                                            | 3  |  |

|   |      | 1.1.2    | The Memory Wall Problem                                               | 6  |  |

|   |      | 1.1.3    | Multicore Architectures                                               | 7  |  |

|   |      | 1.1.4    | Emerging Many-Core Architectures                                      | 9  |  |

|   | 1.2  | Thesis   | Contributions                                                         | 10 |  |

|   |      | 1.2.1    | Mixed Precision Iterative Refinement                                  | 10 |  |

|   |      | 1.2.2    | Co-Processor Acceleration of Existing Large-Scale Codes               | 11 |  |

|   |      | 1.2.3    | GPU-Based Multigrid Solvers on Generalised Tensor Product Domains .   | 12 |  |

|   |      | 1.2.4    | A Short History of GPU Computing                                      | 13 |  |

|   | 1.3  | List of  | Publications                                                          | 14 |  |

|   | 1.4  |          | Outline                                                               | 16 |  |

| 2 |      |          | cal Background                                                        | 19 |  |

|   | 2.1  | Finite 1 | Element Discretisation                                                | 19 |  |

|   |      | 2.1.1    | Variational Formulation of the Poisson Problem                        | 19 |  |

|   |      | 2.1.2    | Choice of Basis Functions and Subdivision of the Domain into Elements | 20 |  |

|   |      | 2.1.3    | Mesh Refinement and Error Analysis                                    | 21 |  |

|   | 2.2  |          | ve Solvers for Sparse Linear Systems                                  | 23 |  |

|   |      | 2.2.1    | Basic Stationary Defect Correction Methods                            | 23 |  |

|   |      | 2.2.2    | Krylov Subspace Methods                                               | 24 |  |

|   |      | 2.2.3    | Geometric Multigrid Solvers                                           | 25 |  |

|   | 2.3  | 8        |                                                                       |    |  |

|   |      | 2.3.1    | Separation of Structured and Unstructured Data                        | 29 |  |

|   |      | 2.3.2    | Parallel Multilevel Solvers                                           | 32 |  |

|   |      | 2.3.3    | Two-Layer ScaRC Solvers                                               | 37 |  |

|   |      | 2.3.4    | Vector-Valued Problems                                                | 39 |  |

|   |      | 2.3.5    | Linearised Elasticity in FEAST                                        | 41 |  |

|   |      | 2.3.6    | Stokes and Navier-Stokes in FEAST                                     | 43 |  |

| 3 | A Sl |          | story of GPU Computing                                                | 47 |  |

|   | 3.1  |          | y GPGPU: Graphics APIs                                                | 47 |  |

|   |      | 3.1.1    | The Graphics Pipeline                                                 | 47 |  |

|   |      | 3.1.2    | Evolution Towards Programmability                                     | 50 |  |

|   |      | 3.1.3    | DirectX 9 GPUs – The First Wave of GPGPU 2003–2006                    | 51 |  |

|   |      | 3.1.4    | Legacy GPGPU Programming Model                                        | 53 |  |

|   |      | 3.1.5    | Bibliography of Relevant Publications                                 | 56 |  |

viii Contents

|   |       | 3.1.6 Restrictions of Single Precision                                 | 9 |

|---|-------|------------------------------------------------------------------------|---|

|   |       | 3.1.7 Example Architecture: NVIDIA GeForce 6                           | 9 |

|   | 3.2   | NVIDIA CUDA and AMD Stream                                             | 2 |

|   |       | 3.2.1 DirectX 10 and Unified Architectures 6                           | 2 |

|   |       | 3.2.2 NVIDIA CUDA                                                      | 4 |

|   |       | 3.2.3 AMD CTM and Stream                                               | 9 |

|   |       | 3.2.4 Bibliography of Relevant Publications                            | 1 |

|   |       | 3.2.5 Double Precision Floating Point Support                          | 3 |

|   | 3.3   | GPUs and Parallel Programming Models                                   | 4 |

|   |       | 3.3.1 GPUs as Parallel Random-Access Machines                          | 4 |

|   |       | 3.3.2 GPUs and Vector SIMD Architectures                               | 5 |

|   |       | 3.3.3 Other Programming Models                                         | 6 |

|   | 3.4   | Future APIs and Architectures                                          |   |

|   |       | 3.4.1 OpenCL and DirectX 11                                            |   |

|   |       | 3.4.2 Intel Larrabee and Future Graphics Architectures                 |   |

|   |       | 3.4.3 CPU and GPU Convergence                                          | 9 |

|   | N #*  |                                                                        | 4 |

| 4 |       | ed and Emulated Precision Methods  Motivation                          |   |

|   | 4.1   |                                                                        |   |

|   |       | 1                                                                      |   |

|   | 4.2   | 4.1.2 Benefits of Emulated and Mixed Precision Schemes                 |   |

|   | 4.2   | 4.2.1 Exact and Redundant Emulation                                    |   |

|   |       | 4.2.1 Exact and Redundant Emulation                                    |   |

|   |       | 4.2.3 Normalisation                                                    |   |

|   |       | 4.2.4 Extensions to Higher Precision and Applicability on GPUs         |   |

|   | 4.3   | Mixed Precision Iterative Refinement                                   |   |

|   | т.Э   | 4.3.1 Background and Related Work                                      |   |

|   |       | 4.3.2 Mixed Precision Iterative Refinement for Large, Sparse Systems 9 |   |

|   | 4.4   | Hardware Efficiency on FPGAs                                           |   |

|   | т.т   | 4.4.1 Field Programmable Gate Arrays                                   |   |

|   |       | 4.4.2 Mixed Precision Solvers on FPGAs                                 |   |

|   | 4.5   | Precision and Accuracy Requirements of the Poisson Problem             |   |

|   | 7.5   | 4.5.1 Influence of the Condition Number                                |   |

|   |       | 4.5.2 Influence of the Approximation Quality                           |   |

|   |       | 4.5.3 Influence on the Convergence Behaviour of Iterative Solvers      |   |

|   |       | 4.5.4 Summary and Conclusions                                          |   |

|   |       |                                                                        |   |

| 5 | Effic | ient Local Solvers on Graphics Hardware 10                             |   |

|   | 5.1   | Introduction and Overview                                              |   |

|   |       | 5.1.1 Chapter Outline                                                  |   |

|   |       | 5.1.2 A Brief Overview of the Code Base                                |   |

|   | 5.2   | Legacy GPGPU: OpenGL Implementation                                    |   |

|   |       | 5.2.1 Implementational Specialisations                                 |   |

|   |       | 5.2.2 Example Operations: Parallel Programming Primitives              |   |

|   |       | 5.2.3 Implementation of Numerical Linear Algebra Operations            |   |

|   |       | 5.2.4 Performance Microbenchmarks                                      |   |

|   |       | 5.2.5 Summary                                                          |   |

|   | 5.3   | Modern GPGPU: CUDA Implementation                                      |   |

|   |       | 5.3.1 CUDA Programming Techniques                                      | 5 |

|     | 5.3.2   | Implementation of Numerical Linear Algebra Operations                  | 129 |

|-----|---------|------------------------------------------------------------------------|-----|

|     | 5.3.3   | Performance Microbenchmarks                                            | 133 |

|     | 5.3.4   | Summary                                                                | 140 |

| 5.4 | Paralle | elisation and Implementation of Preconditioners                        | 142 |

|     | 5.4.1   | Introduction and Preliminaries                                         | 142 |

|     | 5.4.2   | Jacobi Preconditioner                                                  | 143 |

|     | 5.4.3   | Preconditioners of Gauß-Seidel-Type                                    | 143 |

|     | 5.4.4   | Tridiagonal Preconditioner                                             | 146 |

|     | 5.4.5   | Combination of Gauß-Seidel and Tridiagonal Preconditioners             | 153 |

|     | 5.4.6   | Alternating Direction Implicit Preconditioners                         | 154 |

|     | 5.4.7   | Performance Microbenchmarks                                            | 155 |

|     | 5.4.8   | Summary                                                                | 157 |

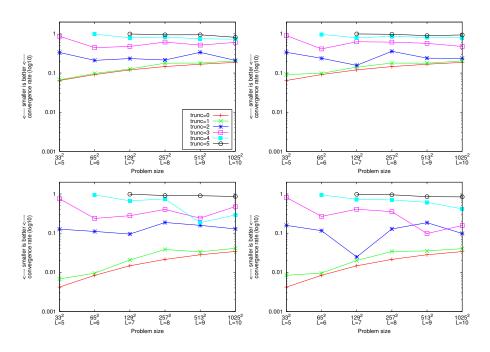

| 5.5 | Numer   | rical Evaluation of Parallelised Preconditioners in Iterative Solvers  | 158 |

|     | 5.5.1   | Overview and Test Procedure                                            | 158 |

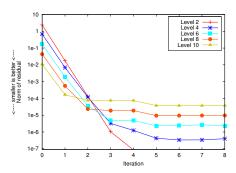

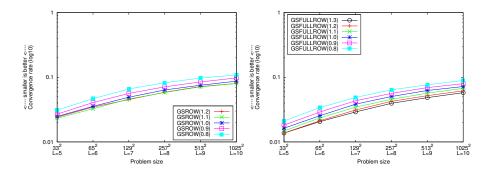

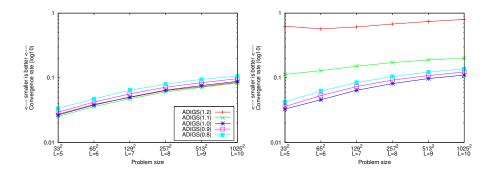

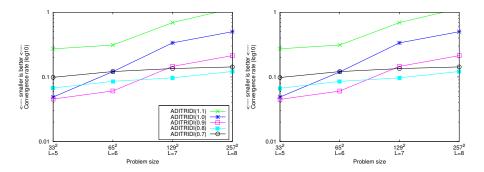

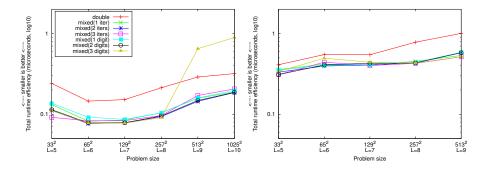

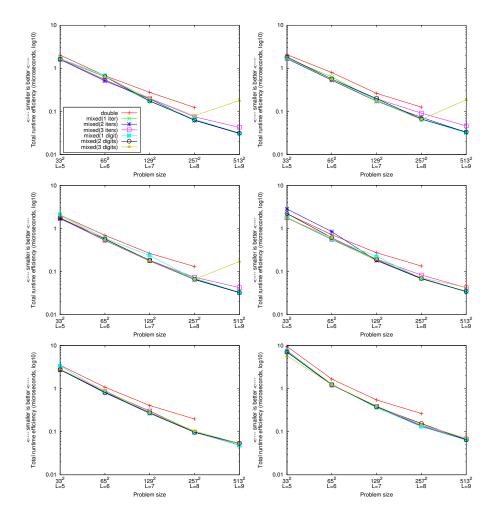

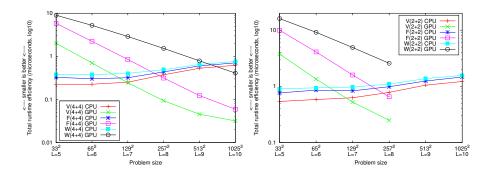

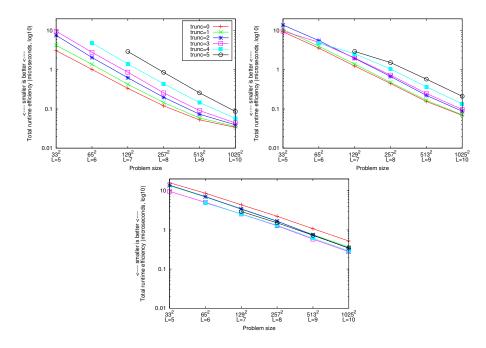

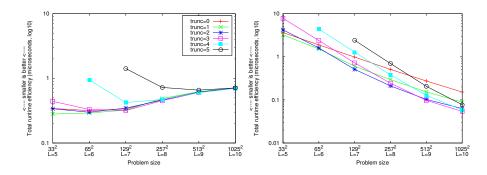

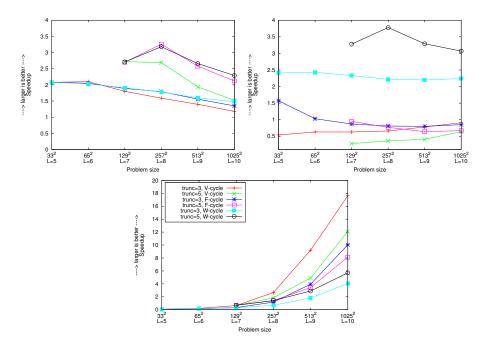

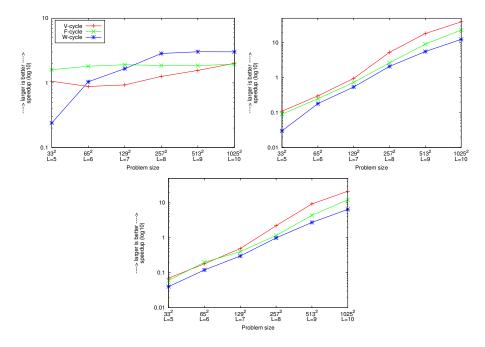

|     | 5.5.2   | Pure Numerical Efficiency of Multigrid Solvers                         | 160 |

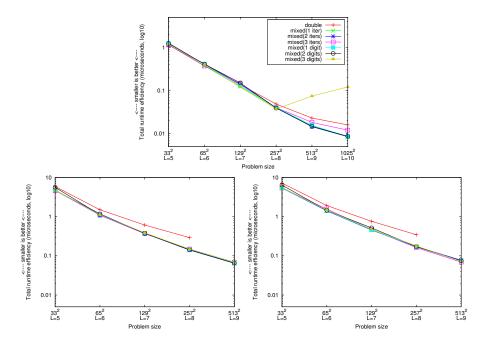

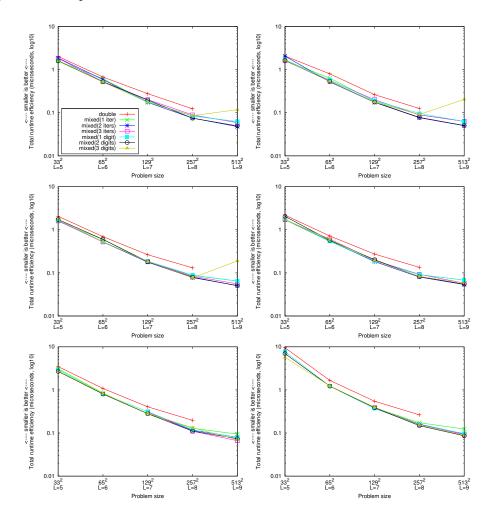

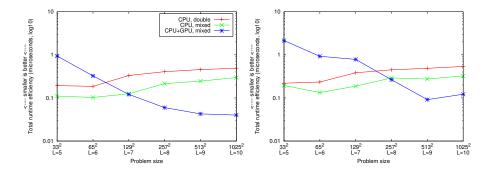

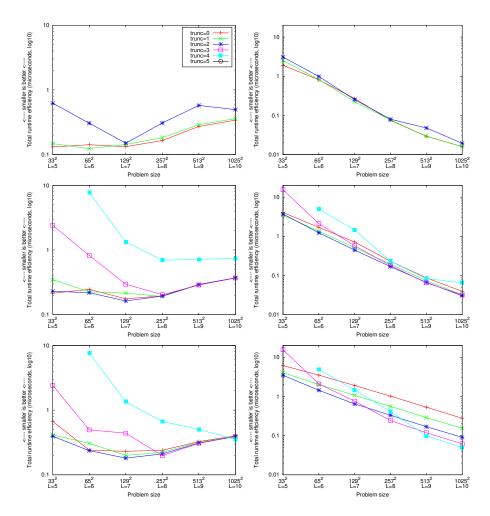

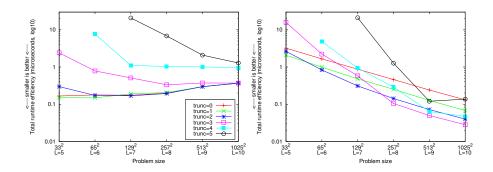

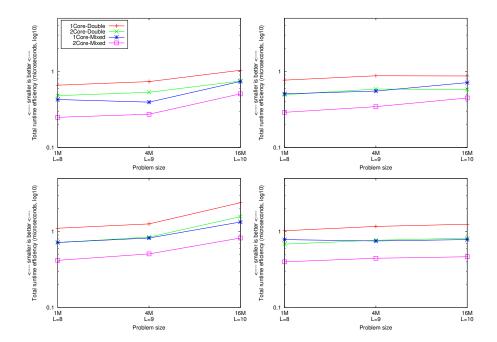

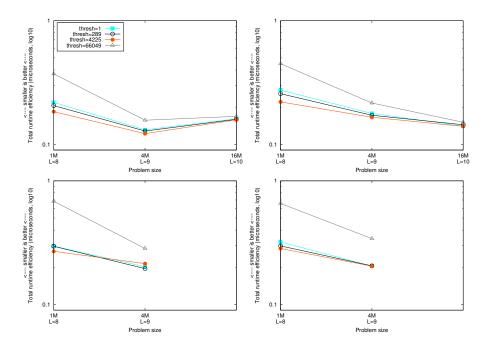

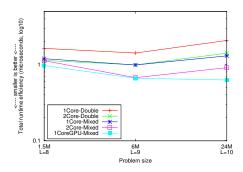

|     | 5.5.3   | Total Runtime Efficiency of Multigrid Solvers                          | 164 |

|     | 5.5.4   | Krylov Subspace Solvers                                                | 168 |

|     | 5.5.5   | Summary                                                                | 168 |

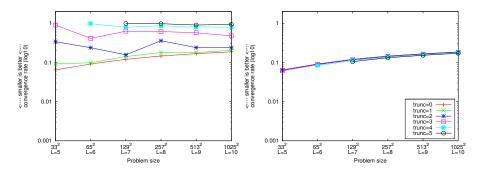

| 5.6 | Accura  | acy of Emulated and Mixed Precision Solvers                            | 171 |

|     | 5.6.1   | Overview and Test Procedure                                            | 171 |

|     | 5.6.2   | Accuracy of Mixed Precision Iterative Refinement Solvers               | 174 |

|     | 5.6.3   | Accuracy of the Emulated Double-Single Format                          | 174 |

|     | 5.6.4   | Summary                                                                | 176 |

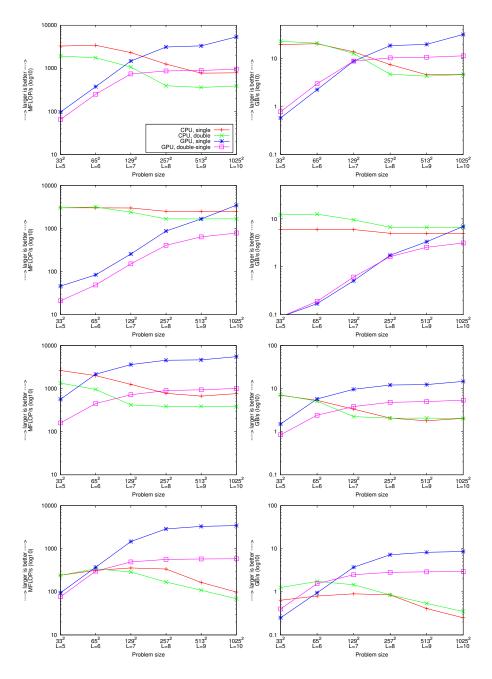

| 5.7 | Numer   | rical Evaluation of Mixed Precision Iterative Solvers                  | 177 |

|     | 5.7.1   | Overview and Test Procedure                                            | 177 |

|     | 5.7.2   | Efficiency on the CPU and Influence of the Stopping Criterion          | 179 |

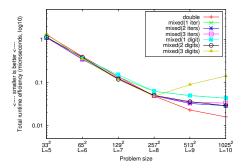

|     | 5.7.3   | Efficiency on the GPU                                                  | 182 |

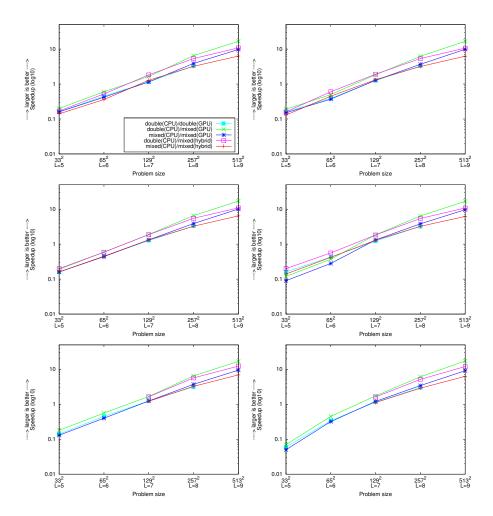

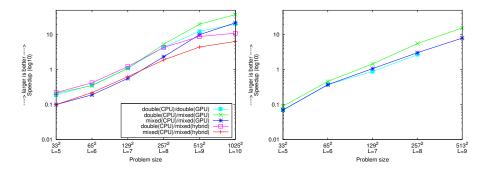

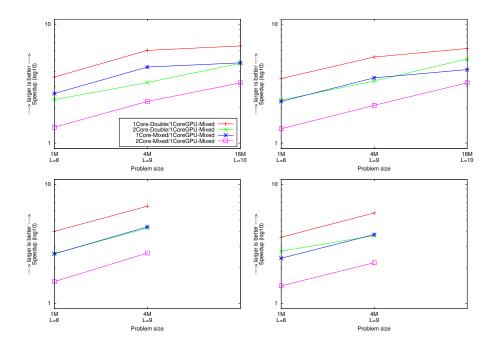

|     | 5.7.4   | Speedup of GPU-based Solvers                                           | 186 |

|     | 5.7.5   | Summary                                                                | 189 |

| 5.8 | Influer | nce of the Multigrid Cycle Type and the Coarse Grid Solver             | 191 |

|     | 5.8.1   | Overview and Test Procedure                                            | 191 |

|     | 5.8.2   | Baseline Experiment – Problem Statement                                | 191 |

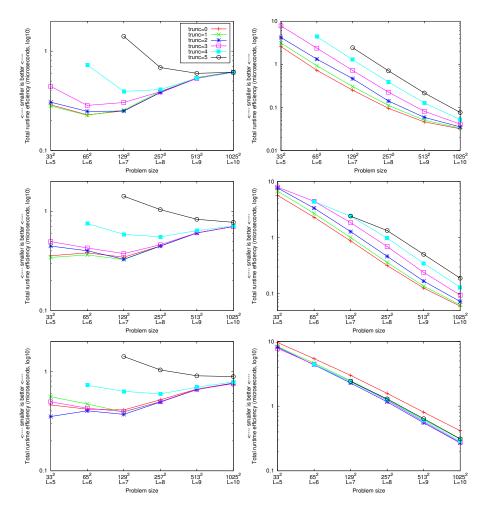

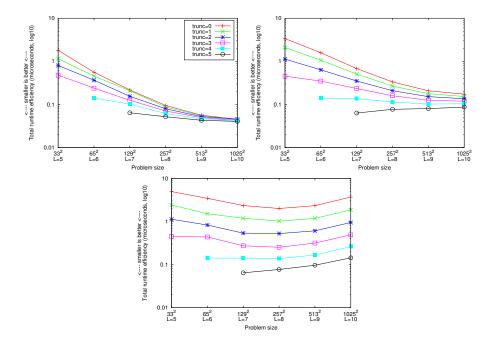

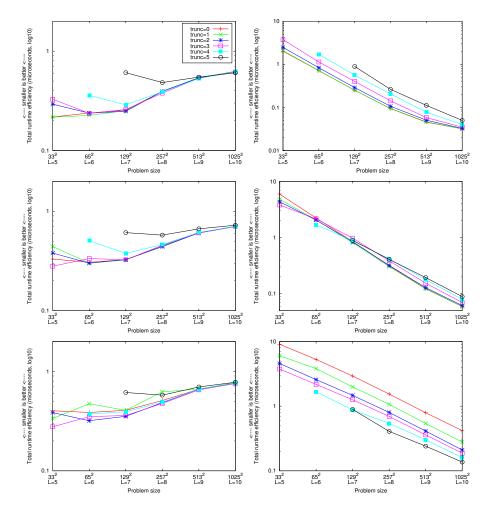

|     | 5.8.3   | Truncation of Multigrid Cycles                                         | 194 |

|     | 5.8.4   | Better Preconditioning of the Coarse Grid Solver                       | 196 |

|     | 5.8.5   | V Cycles with Variable Smoothing: An Alternative to $F$ and $W$ Cycles | 197 |

|     | 5.8.6   | Direct Coarse Grid Solvers on the CPU                                  | 198 |

|     | 5.8.7   | Approximate Solution of Coarse Grid Problems                           | 199 |

|     | 5.8.8   | Implications for Mixed Precision Iterative Refinement Multigrid        | 202 |

|     | 5.8.9   | Summary                                                                | 206 |

| 5.9 | GPU F   | Performance Guidelines                                                 | 209 |

|     | 5.9.1   | Control Flow Between CPU and GPU                                       | 209 |

|     | 5.9.2   | The PCIe Bottleneck                                                    | 209 |

|     | 5.9.3   | GPU vs. CPU Performance Characteristics                                | 210 |

|     | 5.9.4   | Locality, Vectorisation and Memory Access Patterns                     | 211 |

|     | 5.9.5   | Resource Allocation                                                    | 211 |

X Contents

| 6  | Min    | •       | Invasive Co-Processor Integration into FEAST                         | 213   |

|----|--------|---------|----------------------------------------------------------------------|-------|

|    | 6.1    | Introdu | action and Motivation                                                | 213   |

|    |        | 6.1.1   | Motivation                                                           | 213   |

|    |        | 6.1.2   | Chapter Overview                                                     | 215   |

|    | 6.2    | Minim   | ally Invasive Co-Processor Integration into FEAST                    | 217   |

|    |        | 6.2.1   | ScaRC Solver Analysis                                                | 217   |

|    |        | 6.2.2   | Minimally Invasive Integration                                       | 218   |

|    |        | 6.2.3   | GPU Integration Challenges and Implementational Details              | 222   |

|    |        | 6.2.4   | Hybrid Solvers for Heterogeneous Clusters                            | 224   |

|    | 6.3    | Numer   | rical Building Block: Poisson Problem                                | 225   |

|    |        | 6.3.1   | Introduction and Test Procedure                                      | 225   |

|    |        | 6.3.2   | Accuracy and Efficiency of Mixed Precision Two-Layer ScaRC Solvers . | 227   |

|    |        | 6.3.3   | Speedup and Speedup Analysis                                         | 230   |

|    |        | 6.3.4   | Weak Scalability on a Large-Scale Cluster                            | 234   |

|    |        | 6.3.5   | Hybrid CPU-GPU Solvers                                               | 238   |

|    | 6.4    | Applic  | ration Acceleration: Linearised Elasticity                           | 241   |

|    |        | 6.4.1   | Introduction, Test Configurations and Solution Strategy              | 241   |

|    |        | 6.4.2   | Accuracy Studies                                                     | 244   |

|    |        | 6.4.3   | Weak Scalability                                                     | 247   |

|    |        | 6.4.4   | Performance and Speedup                                              | 248   |

|    | 6.5    | Applic  | ration Acceleration: Stationary Laminar Flow                         | 251   |

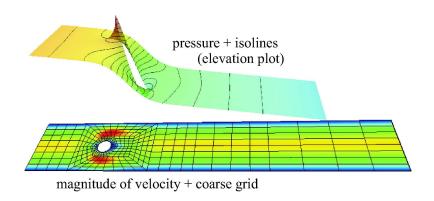

|    |        | 6.5.1   | Introduction, Test Configurations and Solution Strategy              | 251   |

|    |        | 6.5.2   | Analysis of the Linear Solver                                        | 253   |

|    |        | 6.5.3   | Accuracy of the Mixed Precision Stationary Laminar Flow Solver       | 255   |

|    |        | 6.5.4   | Performance Analysis of the Stationary Laminar Flow Solver           | 256   |

|    | 6.6    | Summ    | ary, Critical Discussion, Conclusions and Future Work                | 261   |

|    |        | 6.6.1   | Summary of the Minimally Invasive Integration Approach               | 261   |

|    |        | 6.6.2   | Accuracy                                                             | 262   |

|    |        | 6.6.3   | Weak Scalability                                                     | 262   |

|    |        | 6.6.4   | Performance of Mixed Precision and Accelerated Two-Layer ScaRC Solve | rs263 |

|    |        | 6.6.5   | Critical Discussion in Terms of Future Scalability                   | 266   |

| A  | App    | endix   |                                                                      | 269   |

|    | A.1    | List of | Symbols                                                              | 270   |

| Bi | bliogr | aphy    |                                                                      | 271   |

# 1

# Introduction

This chapter introduces and motivates the (wider) context of this thesis, establishes and summarises its contribution, and provides an outline of the following chapters.

# 1.1. Introduction and Motivation

Scientific Computing is the field of research within applied and numerical mathematics that is concerned with the development, analysis and efficient realisation and implementation of stateof-the-art numerical algorithms on computer systems. In practice, it is very interdisciplinary in nature, because it constitutes an integral part of computational science and engineering (CSE), which bridges the gap between (numerical) mathematics and computer science on the one hand, and on the other hand, all kinds of engineering disciplines. In the context of this thesis, continuum mechanics is of particular interest, i. e., fluid dynamics and solid mechanics. Nonetheless, in academia and in the industry alike, a wide range of application domains are encountered in CSE, ranging from computational chemistry and computational biology (molecular dynamics, genome sequence alignment, drug design) over geophysics (seismic wave propagation, earthquake predictions) to computational finance (risk assessment and trade predictions), to name just a few. Computational science adds *simulation* as the third pillar to science and engineering, between theoretical analysis and experimental verification: Computer systems are used to analyse, to gain understanding and to solve problems from a wide range of application domains. Numerical simulations are often used for economical reasons (when exhaustive experimental analysis is too expensive), or to study phenomena which cannot be accessed in other ways, for instance for the analysis of hazardous substances when experiments are impossible.

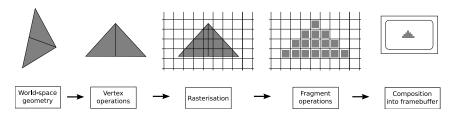

In continuum mechanics, natural phenomena are modeled with fundamental physical conservation laws (e.g., conservation of mass, energy and momentum), expressed mathematically as (systems of) partial differential equations (PDEs) with initial and boundary conditions that stem from experimental measurements or theoretical analysis. The first step in the numerical simulation is the selection of a suitable mathematical model for the problem at hand, for instance the Navier-Stokes equations in the case of fluid flow. Starting from this initial model and an associated set of parameters, a discretisation process is applied to transform the problem from a continuous representation to a finite approximation, in both space and time. After a solution of the discrete problem has been computed, features of interest are extracted either from a visualisation of the results, or by computing characteristic parameters from the solution. Examples in the scope of this thesis include von Mises stresses in solid mechanics (which are an important measure for predicting material failure), or drag and lift coefficients in fluid dynamics. These parameters are then used to refine the initial model, and the process is repeated iteratively.

The wide variety of numerical techniques to solve PDEs is clearly beyond the scope of even these generic introductory paragraphs. In the context of this thesis, it suffices to state that many

techniques boil down to *linear equation systems* that need to be solved repeatedly, and this task is often the most computationally demanding one in the course of a simulation. This is true for instance in the case of implicit time discretisation techniques, or in the case of the Newton-Raphson scheme as an exemplary algorithm for the linearisation of nonlinear problems. We only consider grid-based discretisations like finite elements, differences and volumes, and owing to their strictly local support, the system matrices of these linear systems are very *sparse*, i. e., only a very small number of entries per row is nonzero.

It is obvious that the *computational demands* of CSE workflows of this kind are insatiable. It is not uncommon to face linear systems with billions of unknowns, that need to be solved for thousands of timesteps. Due to the sheer size of the problems, a parallel solution on large supercomputer systems is often unavoidable. *Efficiency* is of utmost importance, in all stages of the solution process:

- Numerical efficiency affects both the discretisation and the solution. Here, we only elaborate upon efficiency aspects of spatial discretisations and the solution of sparse linear systems. Finite element methods are advantageous over finite difference or finite volume approaches in terms of flexibility and accuracy. Furthermore, finite element techniques provide a complete and well-understood theoretical framework which for instance enables rigorous a posteriori error control and thus adaptivity: Less overall unknowns have to be invested for a given target accuracy. For the linear systems of equations encountered throughout this thesis, (geometric) multigrid methods are the most efficient solvers (see Section 2.2): They combine the smoothing properties of inexpensive iterative methods with corrections on a hierarchy of nested coarser grids (coarser representations of the discretised domain), and they converge asymptotically optimal: Computing the solution requires a linear amount of calculations in the number of unknowns, and the convergence rates are provably independent of the mesh width h and thus of the problem size. When equipped with powerful smoothing operators, convergence rates of 0.1 are common, which means that only a small amount of iterations are needed to compute the solution. These favourable theoretical properties should be preserved in practice, no matter if the computation is carried out serially or in parallel. In the latter case, the domain is partitioned into a number of subdomains, and multilevel domain decomposition methods are often applied: For an ideal parallelisation, the convergence rates should be independent of the partitioning of a given domain into subdomains, see Section 2.3.

- The term parallel efficiency refers to how well a given algorithm can be parallelised: In the scope of this thesis, three levels of parallelism are encountered, the coarse-grained parallelism between the nodes in a compute cluster, the medium-grained parallelism between the CPU cores in each node, and the fine-grained parallelism within many-core processors. Each level of parallelism has its own associated communication model, from message passing between distributed memories over (explicit or implicit) locks and mutexes on shared data in global off-chip memory, down to blocks of concurrent threads synchronising via small, on-chip memories. Two important aspects in this context are weak and strong scalability of an algorithm. The former means that when doubling the problem size and the number of compute resources, the time to solution should not change, and the latter means that doubling the amount of resources but leaving the problem size unchanged should lead to a halving of the solution time, i.e., the parallel speedup is linear in the amount of added compute resources. Different levels of parallelism exhibit different communication characteristics, and for perfect both strong and weak scalability, communication must be fully overlapped with independent computations. One may argue that weak scalability can be identified, in terms of convergence rates rather than time to solution, with parallel (numeri-

cal) efficiency: Doubling the number of subdomains and the number of compute nodes but refining each subdomain by the same amount should not change convergence rates.

• Finally, good *hardware efficiency* requires highly optimised implementations, with the goal to extract a significant fraction of the peak performance of modern computer architectures: Hardware efficiency affects both the single-processor performance and the communication characteristics of a given architecture on all levels of parallelism. In practice this means that *high performance computing* techniques, efficient data structures, data layouts and blocking techniques adapted to the memory hierarchy of each architecture must be developed and applied: Different strategies are required for different computer systems and different levels of parallelism.

In practice, these three aspects of efficiency are often mutually exclusive. Algorithms that maximise the numerical efficiency do not necessarily scale well in parallel, and solution techniques exhibiting good strong scaling may converge too slowly for reasonable weak scaling. Different tradeoffs must be taken into consideration for different levels of parallelism, and if hardware efficiency is also taken into account, the search space for an optimally suited algorithm becomes very high-dimensional. Throughout this thesis, we often use the term *computational efficiency* to refer to parallel and hardware efficiency simultaneously. In our group, this field of study is termed *hardware-oriented numerics*, and we discuss its importance in the outset of this thesis in Section 1.1.1.

Obviously, these considerations imply that the different aspects of computational science are strongly interwoven, and scientific computing constitutes more than the sum of its parts from (natural) sciences, computer science, computer architecture and (applied and numerical) mathematics. Consequently, this thesis is also interdisciplinary in nature, and it contributes techniques to improve not only one aspect of efficiency, but techniques to (simultaneously) maximise numerical, parallel and hardware efficiency. In the remainder of this section, we present several instructive examples that help us to motivate the concrete contributions of this thesis which are presented in Section 1.2.

#### 1.1.1. Hardware-Oriented Numerics

Hardware-oriented numerics is, broadly speaking, the combination of high performance numerics and high performance computing, and therefore a subset of scientific computing. We consider a very important example—the solution of a Poisson problem in two space dimensions—to illustrate the core idea of hardware-oriented numerics to *simultaneously maximise numerical and computational efficiency*. This scalar elliptic PDE is a fundamental prototype for all problems encountered and examined in the (wider) scope of this thesis: Poisson problems are encountered in fluid dynamics (pressure-Poisson problem in operator splitting approaches) and solid mechanics (Lamé equations discretised with separate displacement ordering), but for instance also in electrostatics (potential calculations). They are known to be hard to solve, because the condition number of the corresponding discrete linear system depends on the mesh width of the discretisation, which means that they are harder to solve the finer the discretisation becomes (the more accurate the continuous PDE is approximated).

To emphasise the importance of asymptotics, a simple back-of-the-envelope calculation is very instructive; it should of course be taken with a grain of salt: Let us consider a Poisson problem, discretised with bilinear finite elements for a problem size of 1.28 billion  $(1.28 \cdot 10^9)$  unknowns (this is the largest problem solved in this thesis). If one used standard Gaussian elimination to solve the linear system resulting from the discretisation of this problem, and if the system matrix were stored densely, then approximately  $1.4 \cdot 10^{27}$  floating point operations would be needed

for the concrete example at hand: Gaussian elimination to solve a dense linear system with N unknowns executes asymptotically  $2N^3/3 + \mathcal{O}(N^2)$  floating point operations. The RoadRunner system installed at Los Alamos National Laboratory has been the world's first supercomputer to break the petaflops barrier, it is capable of achieving 1.105 PFLOP/s ( $10^{15}$ ) floating point operations per second in the Linpack test. Even with this tremendous level of performance, it would still take more than 40 175 years to solve the problem using Gaussian elimination. The fastest multigrid solver we present for this problem in Chapter 6, which furthermore exploits the sparsity pattern of the system matrix, computes the solution in less than one minute.

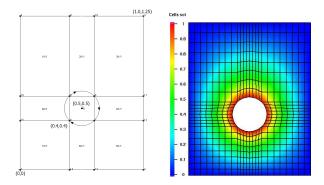

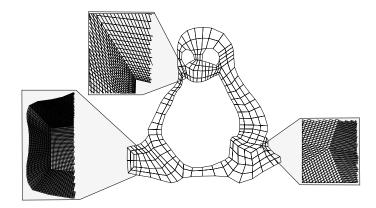

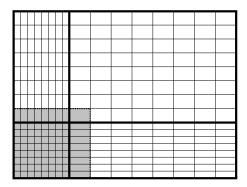

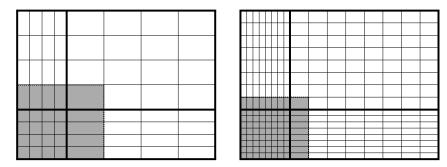

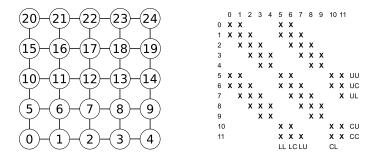

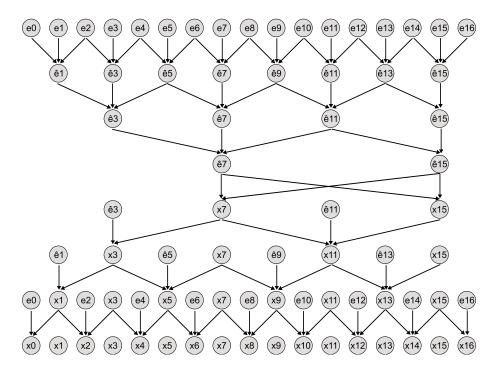

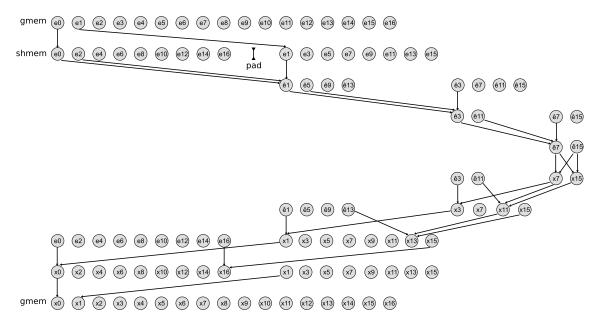

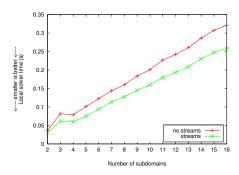

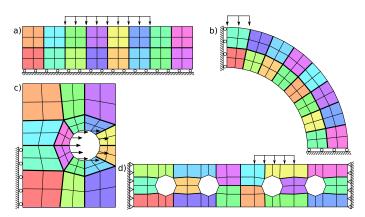

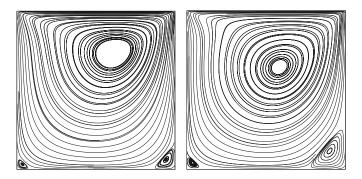

In the following, we consider a prototypical situation that can easily be computed with a conventional, serial code. In Section 2.3 we discuss the aspects of parallel hardware-oriented numerics that are related to distributed memory clusters in detail. Figure 1.1 depicts the (unstructured) coarse grid of this test problem comprising eight elements, and the numerical solution computed on a refined grid. Bilinear quadrilateral conforming finite elements are employed for the discretisation, and uniform refinement is applied so that a *refinement level L* corresponds to  $N = (2^L + 1)^2$  unknowns: For L = 10, the problem size considered in the following, the linear system to be solved has eight million unknowns.

Figure 1.1: Test domain and coarse grid (L=0, left) and computed solution (right) for a simple experiment to demonstrate the ideas of hardware-oriented numerics.

This experiment has been performed in joint work with fellow PhD students [137], and two software packages are evaluated, FEAT and FEAST.<sup>2</sup> FEAT is an established and actively used finite element analysis software package primarily aiming at numerical flexibility and efficiency [27]. FEAST is a next-generation toolkit that prototypically implements many concepts of hardware-oriented numerics. Both packages are actively being developed in our group, and the author of this thesis has contributed significantly to FEAST during the pursuit of this thesis.

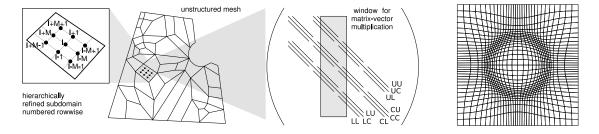

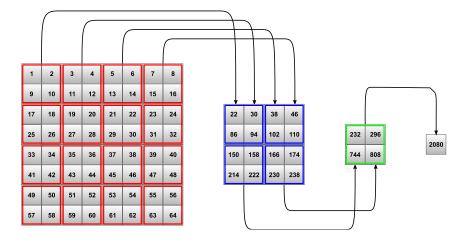

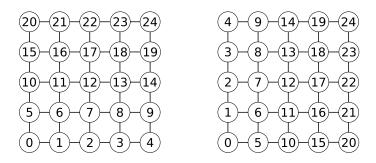

To solve the problem depicted in Figure 1.1, FEAT assembles a global matrix and right hand side, the matrix is stored in the standard *compressed sparse row (CSR)* format,<sup>3</sup> which involves indirect memory accesses to iterate over the nonzero entries. We consider two numbering schemes for the unknowns, a lexicographical enumeration first along the *x*-axis and then along the *y*-axis (denoted as 'XYZ'), and a fully stochastic enumeration. The latter is often used to emulate computations on fully adaptive, highly unstructured grids. We refer to the underlying technical report [137] and to Turek [224] for more details on different numbering schemes, and to the textbook by Saad [191] for a discussion of various sparse matrix storage formats. In contrast, FEAST uses a block-structured approach with (sub-) matrices that correspond to each refined coarse element,

<sup>&</sup>lt;sup>1</sup>See http://top500.org/lists/2008/11 for details.

$<sup>^2</sup>$ see http://www.featflow.de and http://www.feast.tu-dortmund.de

<sup>&</sup>lt;sup>3</sup>In the literature, this format is often also referred to as *compact row storage*, *compressed sparse row* and other acronym permutations thereof.

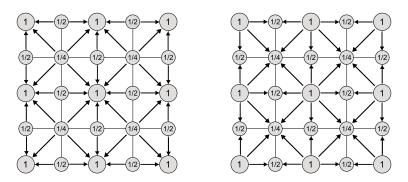

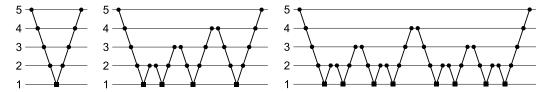

and a linewise numbering in each of these patches (see Section 2.3). The benefit of this approach is that every submatrix has a banded structure, and this special structure is exploited in the design and implementation of numerically and computationally efficient data structures, preconditioners and other operations from numerical linear algebra. In particular, each band is stored as an individual vector, and matrix-vector multiplication does not require 'pointer chasing' through memory. Furthermore, blocking to efficiently exploit cache hierarchies and other aspects of modern processors is enabled by FEAST's approach. In summary, FEAST's discretisation technique is designed around *locally structured, globally unstructured grids* (which does not prevent adaptivity per se), and we refer to Section 2.3 for more background on FEAST.

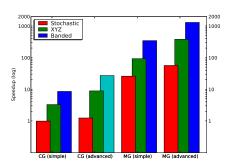

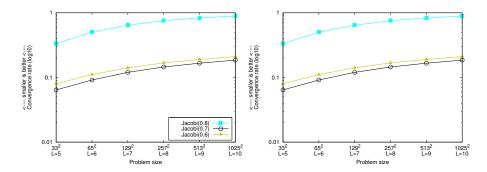

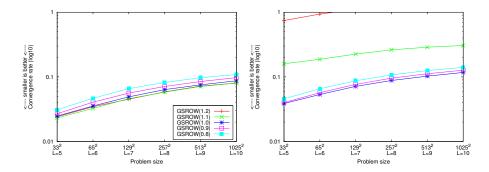

Two different solvers are evaluated, conjugate gradients as a representative of simple Krylov subspace schemes, and multigrid, which is asymptotically optimal for this elliptic problem. In both cases, we employ either a Jacobi preconditioner (labeled simple), or the most numerically and computationally efficient preconditioner available. For the CSR matrices that can incorporate changes of the nonzero pattern easily, preconditioners based on incomplete LU factorisations (ILU) are commonly considered to be most efficient, at least among the techniques that have some kind of black-box character. Preconditioners that maintain the computationally favourable band format are harder to design, and we choose an alternating direction implicit combination of Gauß-Seidel and line-relaxation (ADITRIGS, see Section 2.3 for details). All measurements are obtained on a single core of a compute server equipped with Opteron 2214 processors and fast DDR2-667 memory, a machine that is used frequently throughout this thesis.

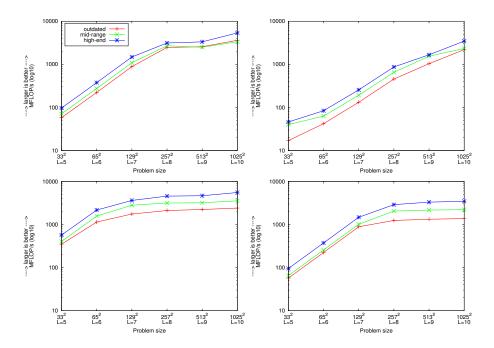

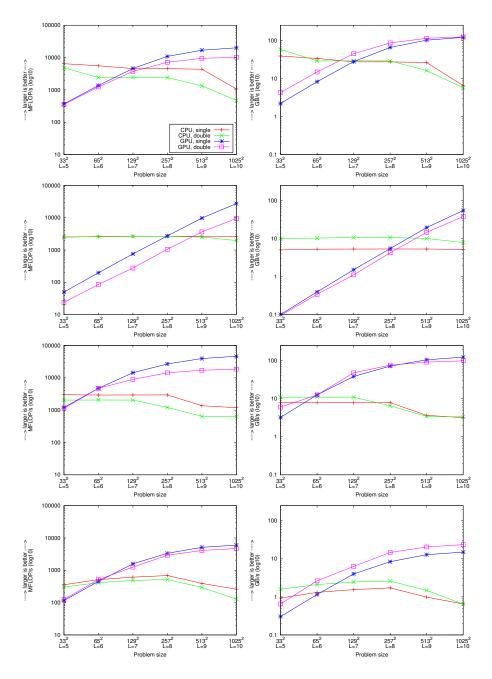

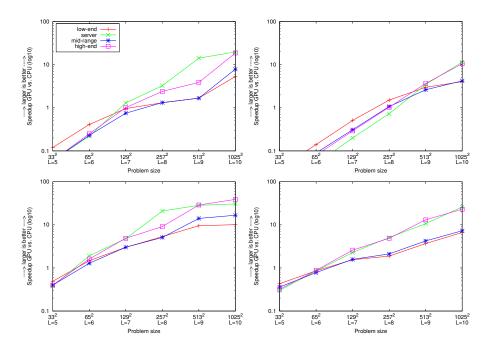

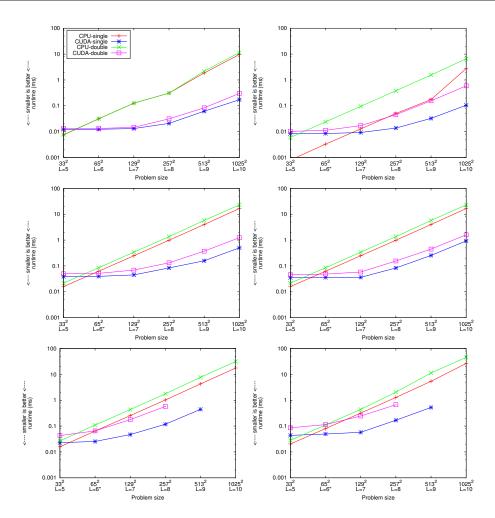

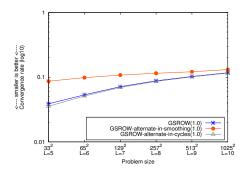

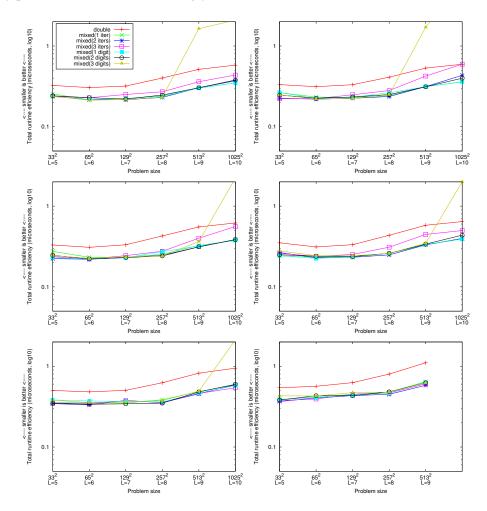

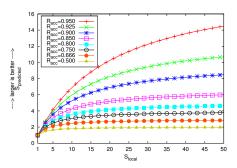

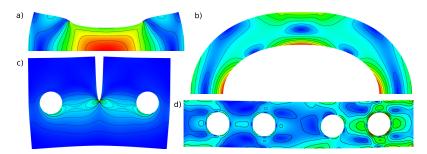

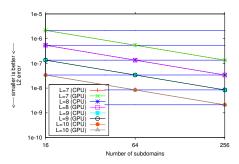

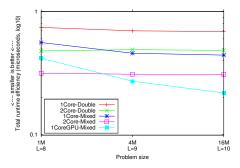

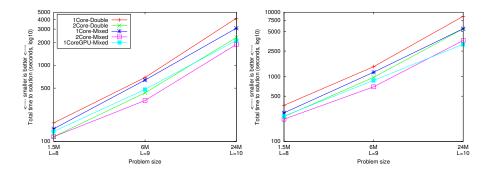

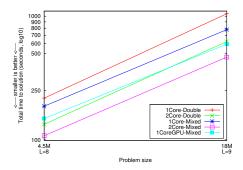

**Figure 1.2**: Relative performance improvement obtained by hardware-oriented numerics for a Poisson problem, normalised timings. The *y*-axis uses a logarithmic scale.

Figure 1.2 illustrates the performance results; as only relative improvements are relevant for the argument in this introductory section, all measurements are normalised to the slowest configuration. The data point for the conjugate gradient solver using an advanced preconditioner for the banded data layout is estimated, because at the time these tests have been performed, a symmetric advanced preconditioner has not been available in FEAST. We first observe that the data layout and the data access patterns are of great importance for the efficiency of algorithms running on modern computer hardware. A simple reordering of the unknowns improves performance by a factor of 3 without changes to the data layout, and better data layouts can gain a factor of 10–30. Very 'bad' data layouts (e. g., stochastic numbering) let the performance drop to a mere 1 % of the theoretical peak floating point throughput of the Opteron processor. The technical report lists all numbers in detail [137]. On the other hand, it is essential that the structure of the mathematical problem does not get lost in the design of the solvers. Utilising a hierarchical solver that exploits multigrid structures quickly pays off and may lead—in combination with the 'correct' data layout—to a speedup by a factor of 1 300 and even more in computation time compared to a straightforward implementation of a simple numerical scheme. An extremely tuned implementation of a

numerically poor algorithm is easily outperformed by a more advanced numerical scheme, so the importance of advanced numerical methodology clearly dominates all implementational aspects. But on the other hand, advanced algorithms implemented without awareness of the underlying machine architecture exhibit degrading performance, as we demonstrate below.

Consequently, our hypothesis is that in the field of high performance finite element simulations, significant performance improvements can only be achieved by maximising computational and numerical efficiency simultaneously: Numerical and algorithmic foundation research must accompany (long-term) technology trends; and prospective hardware trends must enforce research into novel numerical techniques that are in turn better suited for the hardware. This view is shared by many other researchers: Keyes [126] and Colella et al. [50] survey trends towards terascale computing for a wide range of applications including finite element software and conclude that only a combination of techniques from computer architecture, software engineering, numerical modelling and numerical analysis will enable a satisfactory scale-out on the application level, see also the bibliography of work related to FEAST in Section 2.3. The following observation, which motivates hardware-oriented numerics, thus summarises the context of this thesis:

Substantial performance improvements can only be achieved by hardware-oriented numerics, i. e., by simultaneously maximising numerical and computational efficiency.

While these examples and conclusions are all based on serial code, the same line of argument holds for large-scale parallel computations executing on distributed memory clusters. This is an important aspect in view of the contribution of this thesis, but to keep this introduction concise, we do not argue along these lines. The interested reader is referred to the introductory chapters of previous theses on FEAST for motivations which focus on this aspect [15, 130, 242], and to Section 2.3 and the references therein for an overview of FEAST.

# 1.1.2. The Memory Wall Problem

The sustained bandwidth and the latency to access data in off-chip memory is much more important for grid-based codes than the raw compute performance, as the discretisation process leads to large, but very sparse matrices. The *arithmetic intensity*, defined as the ratio of floating point operations per memory access, of computations involving such matrices is very low, commonly less than one. This is problematic, because an access to off-chip memory can cost hundreds of clock cycles, while modern processors are able to execute several arithmetic operations per cycle in their vector units: *Computing is cheap, and data movement is expensive*. This problem is known as the *memory wall problem*, and is further aggravated by the fact that peak processor performance continues to increase at a much faster pace than peak memory bandwidth: Over the past decade, processor speed has been improving at 60 % per year (this is not to be confused with Moore's Law), whereas DRAM access is only getting faster by 10 % anually [97, 134].

The common approach in computer architecture and processor design to alleviate the memory wall problem is to employ ever larger hierarchies of fast, on-chip cache memories. In order to exploit these caches, *data reuse* must be maximised on the software side. In view of hardware-oriented numerics, techniques like temporal and spatial blocking have been developed to keep data in-cache for as long as possible. In combination with vectorisation techniques, efficient block-memory transfers that better exploit the available bandwidth are enabled. Similarly, current processors support asynchronous prefetching of data between different memory levels. Section 2.3 provides references to early and recent work on the topic. These observations lead to the second fundamental motivation for the work presented in this thesis:

Memory performance and memory performance optimisations are much more important than (peak) compute performance for sparse codes.

#### 1.1.3. Multicore Architectures

Software development for finite element problems, driven by the mathematical community, is traditionally focused on the improvement of the numerical methodology. For instance, adaptivity techniques, higher order discretisations, and a wide range of stabilisation approaches are being used, developed and refined. Hardware aspects used to play only a minor role, since codes automatically ran faster with each new generation of processors during the past decade. This trend has come to an end, because physical limitations have led to a paradigm change in processor architectures: Aggressively optimising circuits, deep processor pipelines and in particular large on-chip cache memories have increased the power requirements and consequently the heat dissipation beyond acceptable scales, both for supercomputing architectures and for commodity processors. Furthermore, leaking voltage in high-end chip designs has become a problem that is increasingly hard to alleviate. These aspects are commonly summarised with the term power wall, hardware designers are able to put more transistors on a chip than they can afford to turn on. As a consequence, frequency scaling is limited to 'natural frequency scaling' by process shrinking; the reduction in feature size is, roughly speaking, proportional to the number of admissible transistors under a fixed power budget. Performance can no longer be improved by simply increasing the CPU clock frequency. On the other hand, ever wider superscalar architectures with more aggressive out-oforder execution have reached their limits as well, the hardware is no longer able to extract enough instruction-level parallelism to hide latencies (ILP wall). An important consequence is:

Together, the power wall, the memory wall and the ILP wall form an 'impenetrable brick wall' for serial legacy codes [8].

Processor manufacturers have begun to migrate towards on-chip parallelism in the form of *chip multiprocessors (CMP)*, these designs are more commonly known as *multicore architectures*: The (approximately) doubled amount of transistors per chip generation (Moore's Law) is invested into a doubling of processing cores. This trend has reached the mass market in 2005, when both AMD and Intel introduced commodity multicore CPUs with their Athlon 64 X2 and Pentium D chips. At the time of writing, quadcore processors are standard, and the first six- and eight-core designs are appearing. As a consequence, the performance of each individual core is remaining constant or even degrades, which leads us to the next important motivation of this thesis:

Single-threaded legacy codes no longer run faster automatically.

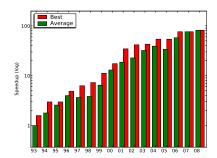

We illustrate this important observation based on FEATFLOW [225], a CFD solver built on top of FEAT which has already been used for the experiment presented in Section 1.1.1. FEATFLOW draws its strength from state-of-the-art numerical techniques and a flexible design to facilitate the straightforward addition of novel finite-element related functionality, but its implementation is 'typical' for the mathematical community in the sense that it does not include hardware-specific optimisations at all: Standard data structures like CSR to store sparse matrices are employed, and all optimisations are left in the responsibility of the compiler. In addition, FEATFLOW is strictly single-threaded. Since the early days of its development 15 years ago, FEATFLOW contained a suite of well-defined CFD benchmarks, and the project website<sup>4</sup> lists timing results on workstations constituting the state of the art during these years. Figure 1.3 depicts the relative performance gain based on this benchmark data. In the covered time frame from 1993 to 2008, hardware progress (and associated improvements in compiler technology) delivered a speedup by a factor of 80, essentially for free. While this number is indeed impressive, CPU peak performance in these 15 years increased more than 1 000-fold. The reason for this discrepancy is the memory

<sup>4</sup>http://www.featflow.de

wall problem, see Section 1.1.2. However, the important observation in the outset of this thesis is that the *free* performance gain has begun to stagnate with the advent of multicore processors. We observe this postulated consequence in an established code already, and not in (artificially constructed) microbenchmarks.

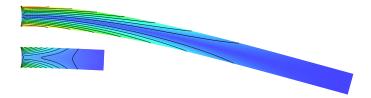

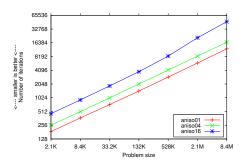

**Figure 1.3**: Normalised performance of the single-threaded FEATFLOW benchmark, 1993–2008. The bars labeled 'best' represent the fastest machine up to a given year, and the bars labeled 'average' correspond to the averaged performance of all machines evaluated in one year. The y-axis uses a logarithmic scale.

#### **Consequences for Numerical Codes**

This development shifts most of the responsibilities to maximise efficiency and, more importantly, scalability and usability of a given software on future hardware generations from the hardware architects and the compiler community to the software developer: Task and data parallelism must be exploited not on the level of coarse grained parallelism (compute nodes in a distributed memory cluster), but explicitly at a finer scale:

The evolution towards on-chip parallelism is evident, and exploiting it is in the responsibility of the software developer.

Multicore designs significantly increase the peak compute performance from one hardware generation to the next, because the number of cores increases exponentially. At the same time, memory performance continues to improve at a significantly slower rate. Due to *pin limits* (the limited amount of physical data paths to move data from off-chip memory to the processing cores), the memory wall problem is even worsened by multicore architectures: With memory controllers moving on-chip and core counts increasing rapidly, more and more parallel computations have to compete for the limited bandwidth to off-chip memory, which often scales with the number of sockets per compute node rather than the number of cores per processor [241]. In addition, memory access speed becomes increasingly non-uniform, as on-chip cache memories used for fast data exchange between cores are not shared by all cores, and on-chip memory controllers maintain only their local portion of main memory. This leads us to the final observation to be taken into account in the work presented in this thesis:

In conventional general-purpose architectures, the trend towards on-chip parallelism aggravates the memory wall problem and prevents future scalability of legacy finite element codes.

In high-performance computing, innovations stemming from research on *symmetric multiprocessing (SMP)* shared memory systems during the last decade have lead to the development of

libraries and programming environments to exploit the parallelism within a compute node, the most prominent example is OpenMP.<sup>5</sup> OpenMP enables the programmer to declare parallelism by explicitly inserting certain preprocessor statements into the code. Many current research efforts aim at bridging the gap between SMP and CMP systems, in particular in view of the non-uniform memory characteristics mentioned above. It is important to note that at the time of writing, compiler support to automatically parallelise a given finite element code using threads is still in its infancies because this task requires global knowledge of the data flow, which is hard to extract by compilers acting locally on the instruction stream. Efficient autoparallelisation is not expected in the medium term [8].

# 1.1.4. Emerging Many-Core Architectures

In this thesis, we go one step further and do not consider multicore CMP parallelism, but rather the massively fine-grained parallelism exposed by unconventional yet promising *emerging manycore* architectures. Currently available multimedia processors such as the Cell BE processor and—in particular—*graphics processing units* (*GPUs*) have gained increasing interest in view of the above mentioned trends and issues. In fact, they are considered as forerunners of these trends, and are commonly labeled emerging many-core architectures, a nomenclature we follow throughout this thesis. This observation makes these chip designs very attractive outside their traditional application domains, for general-purpose and (in the scope of this thesis) high performance numerical computations. The author of this thesis has actively researched the potential of these architecture for finite element computations since 2005, see also Section 1.2. GPUs in particular alleviate many of the issues by their fundamentally different processor design, because they exploit parallelism to a much greater extent than conventional CPUs, and because they are optimised for maximising throughput of a given computation rather than latency of an individual operation. This is achieved by *massive hardware multithreading*, in combination with a parallel memory subsystem.

As a concrete motivation, we list several important features of the NVIDIA GeForce GTX 280 graphics accelerator, the most powerful GPU employed throughout this thesis: Its 30 so-called multiprocessors ('cores') and its 512 bit interface to main memory result in rather impressive peak numbers of over 1 TFLOP/s raw compute performance and 140 GB/s of bandwidth to fast off-chip memory, at least an order of magnitude higher than conventional designs. A single such graphics board consumes 236 W under full load, and costs less than 400 Euro, placing it at the 'bleeding edge' not only in raw peak numbers, but also in increasingly important metrics such as performance/Watt and performance/Euro. In view of the memory wall problem, it still costs approximately 600 clock cycles to access data in off-chip memory, but these GPUs can 'hide' this latency via a very efficient lightweight thread scheduling mechanism implemented directly in hardware, keeping more than 30 000 threads 'in-flight' simultaneously. For comparison, HyperThreading technology in current quadcore CPUs maintains two threads per core. Stalled threads waiting for memory transactions are suspended, and automatically resumed once the data is available. In essence, GPUs are specialised for high throughput rather than minimisation of latencies for random access, they excel at data-parallel computations. It is worth noting that the multi-billion dollar market of video games entails rapid evolution and superlinear performance improvements across chip generations at comparatively low acquisition costs, in contrast to more specialised solutions aiming at the HPC market alone.

In the next section, we describe how the development towards fine-grained parallelism lead to the contribution of this thesis.

<sup>5</sup>http://openmp.org/

# 1.2. Thesis Contributions

The main contribution of this thesis, in view of the paradigm shift outlined in Section 1.1, is to demonstrate that *GPUs as current representatives of emerging many-core architectures are very well-suited for the fast and accurate solution of PDE problems*, in particular for the solution of large sparse linear systems of equations on large compute clusters: We report on at least one order of magnitude speedup over highly-tuned conventional CPU solutions, *without sacrificing neither accuracy nor functionality*. This improvement in performance is achieved over an already highly optimised, numerically and computationally efficient implementation that follows the concept of hardware-oriented numerics, see Section 1.1.1. Speedups of this order are highly relevant in practice, because the asymptotical 'free' speedup for bandwidth-limited codes is a mere 10% per year [97], see also Section 1.1. This contribution is achieved by combining techniques from numerical mathematics *and* computer science to design algorithms and data layouts that efficiently exploit fine-grained parallelism, and to design numerical schemes that scale perfectly with thousands of concurrently active threads. Consequently, this thesis as a whole is interdisciplinary in nature.

The individual contributions of this thesis are summarised thematically below. In addition, we provide pointers to later sections which explain the results in detail. Section 1.3 presents our contributions in a chronological fashion by listing the (peer-reviewed) articles and conference proceedings that have been published in the pursuit of this thesis to disseminate results and novel contributions in a timely manner. Finally, Section 1.4 provides a linear sorting of the topics covered in this thesis. We summarise this thesis at three different angles to make the contents as accessible as possible.

#### 1.2.1. Mixed Precision Iterative Refinement

Floating point arithmetic on computer systems provides finite, limited precision, and computational precision and result accuracy are related in a highly unintuitive, 'nonlinear' way. An important theoretical result states that the condition number of a linear system essentially determines the (minimally) required computational precision to deliver an accurate result. Due to truncation and cancellation errors, this theoretical result however does not tell the whole story. For all problems considered in this thesis, i. e., for the prototypical Poisson problem, for linearised elasticity and for stationary laminar flow, the condition number of the system matrix depends on the discretisation mesh width, and thus deteriorates with increasing problem size. We demonstrate that already for simple test cases that do not involve complex geometries, anisotropic and/or locally adapted grids, standard single precision floating point arithmetic may be insufficient and lead to wrong solutions, see Section 4.5.

Mixed precision methods have been known for more than 100 years already. They have gained rapid interest with the arrival of computer systems in the 1940s to 1960s. At that time, floating point computations had been much more expensive than memory accesses. The idea of these methods is to iteratively improve a solution computed in low precision, by using a high precision defect correction loop: The majority of the computations are carried out in cheaper low precision. To maximise efficiency, one obviously wants to execute as many operations as possible in a floating point format that is *natively* supported in hardware. If the problem at hand is 'not too ill-conditioned' in low precision, iterative refinement provably converges to high precision accuracy. Not natively available higher precision formats can also be emulated in software, for instance with the so-called double-single technique (native pair arithmetic), which uses only natively available arithmetic operations.

Since that time, mixed precision iterative refinement has received little attention in the community. The commonly applied procedure has become, in the past 20 years, to execute all computa-

tions entirely in double precision, the highest precision natively available in commodity hardware. This is an immediate consequence of the fact that, for a wide range of practical problems, double precision yields sufficient accuracy.

However, double precision may not be available on some hardware, or may be significantly slower. In view of the memory wall problem, using single precision is also advantageous, because the bandwidth requirements are halved, and twice the amount of data can be stored at each level of the memory hierarchy. In this thesis, we therefore revisit these techniques from a memory performance perspective, which has not commonly been done in the past years. Chapter 4 is dedicated to this contribution: The theoretical foundation of mixed precision methods is based on the exact solution of the auxiliary low precision problems, which is not possible in our context where approximate, iterative methods for the large, sparse systems have to be employed. After reviewing related work and the theoretical background, we present a mixed precision iterative refinement framework that is specifically designed for this situation: An outer iterative refinement loop is preconditioned with an inner multigrid or Krylov subspace solver.

We thoroughly analyse our method with a wide range of numerical experiments in a variety of different contexts in Sections 5.6–5.8 and Sections 6.3–6.5. In particular, we demonstrate the following important findings: Even for severely ill-conditioned problems (condition numbers on the order of 10<sup>15</sup>), our mixed precision solvers always compute the same result as if computing entirely in double precision. This is not the case when using an emulated precision format based on the unevaluated sum of two native single precision values. When employing multigrid to approximately solve the auxiliary problems to no more than two digits accuracy, we obtain a speedup of 1.7–2.1 over executing entirely in double precision, on CPUs and on GPUs. The combination of these two results means that mixed precision iterative refinement, executing hybridly on the CPU and on accelerators that do not support double precision at all, is the only viable approach to exploit the performance of such hardware without sacrificing accuracy for the problems examined in this thesis. Reducing the residuals further is, in contrast to theory that is based on exact solutions, not beneficial because the inner solvers converge to wrong solutions in single precision or may not converge at all. The speedup is in line with the bandwidth considerations outlined above, and underlines the increased efficiency of our solvers.

Furthermore, even though we do not examine this aspect in detail, the mixed precision approach is very beneficial for problems that are too ill-conditioned even for (native) double precision. A higher-precision format has to be emulated expensively in software, and analogously to the case of double and single precision examined in this thesis, minimising the amount of arithmetic work performed in the expensive format is beneficial for the overall execution time.

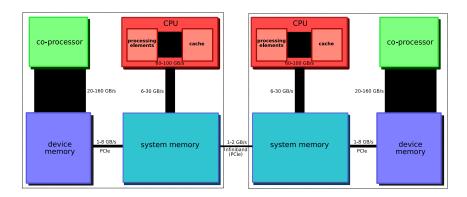

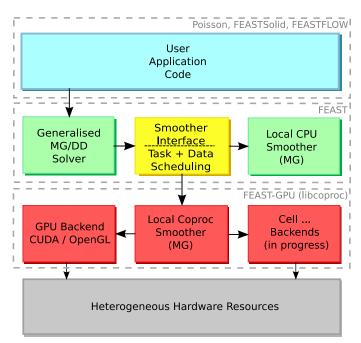

# 1.2.2. Co-Processor Acceleration of Existing Large-Scale Codes

The parallelisation and specialisation of resources as observed in many-core processor designs results in a major challenge for the programming model, in particular for clusters and supercomputers where the coarse-grained parallelism (handled by message passing among distributed memory nodes) must interact with the fine-grained parallelism in co-processors and the increasing heterogeneity (and medium-grained parallelism) within each compute node. In Section 6.1 we argue that re-implementations of codes for each emerging new architecture are prohibitively expensive.

In view of these challenges, an important contribution of this thesis is a *minimally invasive* method to incorporate unconventional and emerging hardware into the existing large-scale finite element toolkit FEAST, which we consider typical in this context (even though it is, at this point, 'only' a research code). This contribution bridges the gap between numerical mathematics and software engineering. FEAST [15] comprises more than 100 000 lines of code in its core modules already; Section 2.3 describes its design and implementation in detail. It is designed around

a multilevel, multilayer domain decomposition approach called SCARC [130] and executes on large commodity based clusters and supercomputers. In two other theses, FEAST has been extended by applications for the challenging large-scale solution of solid mechanics [242] and fluid dynamics [44] problems.

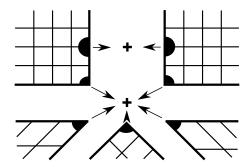

The core idea of our approach is to take advantage of the multilayer SCARC scheme that clearly separates the 'outer' MPI layer from the 'inner' local layer: We offload the entire local work of the Schwarz preconditioner onto co-processors, and leave the 'outer' layer unchanged. The proposed methodology is described in Chapter 6, and has two important advantages: First, it encapsulates the heterogeneities within each compute node so that MPI sees a globally homogeneous system; and second, applications built on top of FEAST benefit from the acceleration through (unconventional) fine-grained parallel co-processor hardware without any code changes.

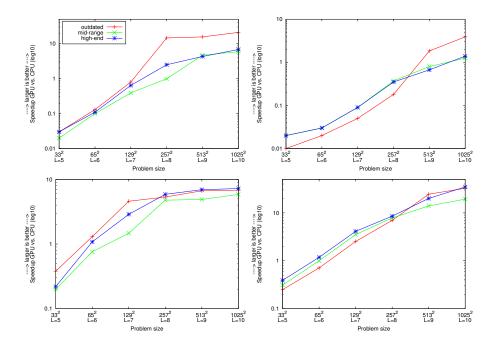

We have implemented this approach, prototypically using GPUs as co-processors (see also the next Section 1.2.3). The resulting 'FEASTGPU' extension of FEAST enables the execution of large-scale computations on heterogeneous GPU-enhanced clusters. We present substantial performance improvements (in terms of time to solution and energy efficiency) for the prototypical Poisson problem, and the two FEAST applications FEASTSOLID and FEASTFLOW (cf. Sections 6.3-6.5), for computations on clusters ranging from 4 to 160 GPUs. Furthermore, we analyse hybrid solvers that simultaneously perform work on the CPUs and the GPUs. Excellent weak scalability is demonstrated on a cluster of 160 GPU-enhanced nodes. We show that the mixed-precision two-layer SCARC scheme, analogous to the small-scale experiments summarised in Section 1.2.1, is faster and delivers exactly the same accuracy as if computing in double precision alone, for large-scale computations with up to one billion unknowns for challenging problems from linearised elasticity. As we only accelerate portions of the entire solver, the speedup is limited by the fraction of time spent in the unaccelerated parts. Depending on the concrete configuration, we accelerate between 50 and 90 % of the entire solution scheme, so the total speedup is bounded between factors of 2 and 10. We develop an analytical model similar to Amdahl's Law to predict the total speedup based on this accelerable fraction (which is a property of the unmodified CPU-based code) and the local speedup (which can be measured in local solver benchmarks, see Section 1.2.3), and show that the predicted values are recovered in the experimental results.

# 1.2.3. GPU-Based Multigrid Solvers on Generalised Tensor Product Domains

The third contribution of this thesis is concerned with scalable fine-grained numerical and computational parallelisation techniques for emerging many-core architectures. We develop algorithms to efficiently solve sparse linear systems using multigrid and Krylov subspace methods on GPUs, specifically tailored to finite element discretisations on generalised tensor product domains. These solvers constitute the main building block in the scope of our minimally invasive co-processor acceleration outlined in the previous section. The presented techniques are not limited to finite element based discretisations, but rather applicable for similar grid-based techniques like finite differences or finite volumes.

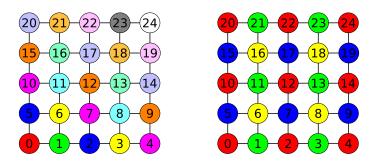

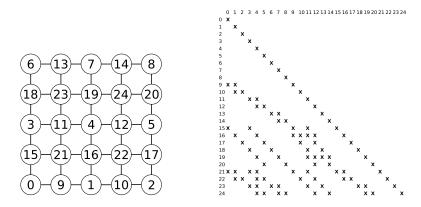

Many of the required operations parallelise in a straightforward manner, at least after suitable, nontrivial reformulations, or by applying reduction techniques. We describe these algorithms for both the 'legacy' GPU programming model of using graphics APIs, and for the 'modern', more powerful NVIDIA CUDA architecture. However, numerically strong preconditioners and multigrid smoothing operators, which are required for challenging problems and high degrees of mesh or operator anisotropy, exhibit recursive, inherently sequential data dependencies, and their parallelisation is thus very challenging. In Section 5.4 we contrast (exact) wavefront with (inexact) multicolouring techniques to parallelise such preconditioners. Only the latter are well-suited for the GPU architecture in our case because they exhibit a sufficient amount of independent paral-

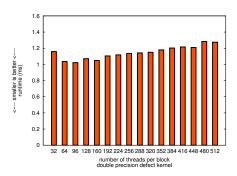

lelism. We develop a favourable renumbering technique for Gauß-Seidel type preconditioners that alleviates many of the disadvantages induced by the lesser degree of coupling inherent to multicolouring. Furthermore, we present an efficient implementation of cyclic reduction for parallel line relaxation preconditioning (the solution of tridiagonal linear systems).

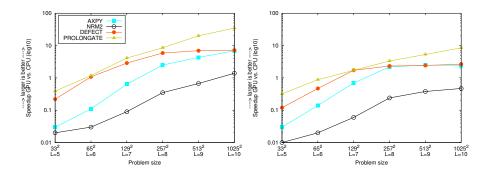

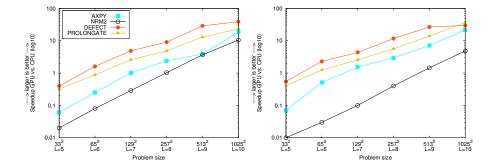

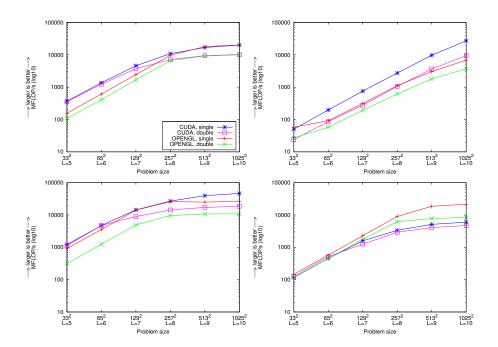

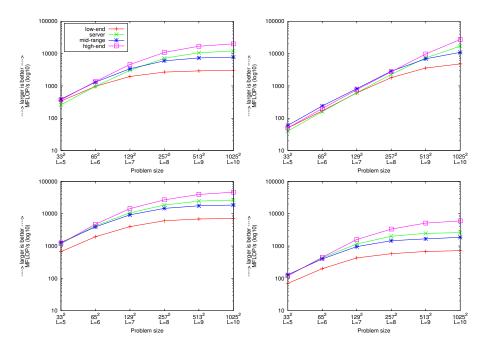

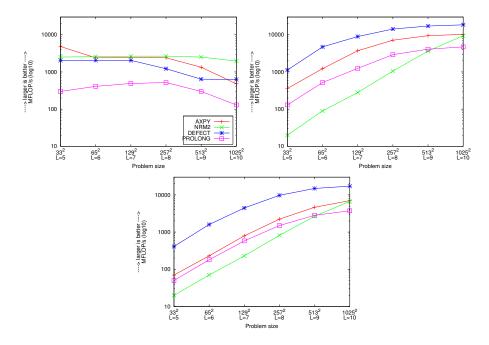

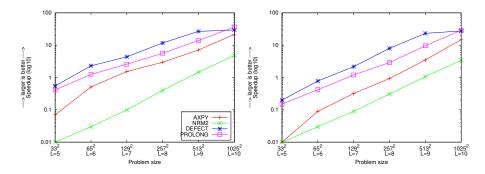

We thoroughly analyse the numerical and computational efficiency of these solvers in Sections 5.5–5.8, in combination with mixed precision iterative refinement methods. Our most important results are: Multicolouring reduces the numerical efficiency of a multigrid solver, but our favourable renumbering scheme almost recovers the convergence rates of the sequential case. For 'simple' preconditioners, we achieve speedup factors of at least one order of magnitude over optimised CPU code, and in many cases, the speedup is even 20- to 40-fold. *F* and in particular *W* cycle multigrid reduces the achievable speedup significantly, due to the amount of time spent on coarser levels of refinement where simply not enough independent parallelism is available to saturate the GPU. We concisely summarise our findings by comparing (well-known) CPU performance characteristics and guidelines with the GPU case in Section 5.9.

# 1.2.4. A Short History of GPU Computing

During the pursuit of this thesis since early 2005, the view of GPUs as many-core processors has changed frequently, and the underlying programming model to exploit fine-grained parallelism has been continuously adapted to technological advancements. When the author started his venture into GPU computing (also known as general purpose computations on GPUs (GPGPU)), this field of research had been obscure, and only few researchers had driven it forward. In these days, GPU computing was commonly identified with a rather ad-hoc, 'hacky' approach and a general 'proof of concept' attitude, mostly because fundamental algorithmic research had to be 'hidden' behind using graphics APIs to indirectly program the device. Nonetheless, GPU computing has gained significant momentum since these early days, and has evolved into an established research area. Hardware vendors have recognised the benefits of GPU computing and have provided high-level programming environments to express parallelism more efficiently. GPU computing is nowadays no longer restricted to academia; commercial products and applications are beginning to appear. A noteworthy contribution of this thesis is thus our historical survey of the evolution of GPU hardware and GPU computing in Chapter 3, with a special focus on the numerical simulation of PDE problems and sparse problems in general. In this chapter, we also explain architectural differences between CPU and GPU processor designs, and discuss why GPUs are a well-suited architecture for data-parallel numerical computations.

# 1.3. List of Publications

During the pursuit of this thesis, the author has published and contributed to a number of peer-reviewed book chapters and journal articles, and intermediate results have been presented at international conferences and published in peer-reviewed proceedings volumes. As GPU computing evolved rapidly during the pursuit of this thesis, early dissemination of novel contributions has been and remains very important. In the following, we list these publications chronologically, ordered by publication type, and link them to the various sections (and covered topics) of this thesis.

The author of this thesis is convinced that research (in scientific computing and elsewhere) is fostered *only* by group efforts, and consequently, all publications listed below have been written in close collaboration with a number of co-authors. This is particularly true for large-scale software projects like FEAST, which involve a large amount of cooperative programming effort: Different publications concerning different aspects and features take different angles, and the order in which authors are listed varies. Lead-authorship in each of the publications below implies that the main novel contribution is attributed to the author of this thesis. But, and this is very important, without the preceeding and joint work within the FEAST group (Susanne Kilian, Christian Becker, Sven Buijssen and Hilmar Wobker) and the collaborations with colleagues (Robert Strzodka, Jamaludin Mohd-Yusof and Patrick McCormick, and Dimitri Komatitsch, Gordon Erlebacher and David Michéa), most of the publications would not have been possible at all. We owe gratitude to all collaborators, and their contribution is gratefully acknowledged.

# **Book Chapters**

In an upcoming textbook tentatively titled *Scientific Computing with Multicore and Accelerators* and scheduled for publication in late 2010, one chapter will describe FEAST and the GPU-acceleration of FEAST developed by the author of this thesis (see Chapter 6). This chapter has been co-written by the entire currently active FEAST group at TU Dortmund: Stefan Turek, Sven Buijssen, Hilmar Wobker and the author of this thesis [234]. A second chapter, co-authored with Robert Strzodka [81], describes fine-grained parallelisation techniques for numerically strong preconditioners in mixed precision multigrid solvers. The contents of this chapter can best be summarised as a 'didactically enhanced' version of Section 5.4 of this thesis.

#### **Journal Articles**

At the time of writing, five journal articles have been published, and three additional ones have been accepted but have not been published yet.

Our first journal article appeared in the *International Journal of Parallel, Emergent and Distributed Systems* in early 2007, co-authored with Robert Strzodka and Stefan Turek. It surveys hardware accelerators, and evaluates native, emulated and mixed precision iterative solvers for sparse linear systems [85]. It constitutes a significantly extended and expanded update of our very first conference proceedings paper [82] which has been, to the best of our knowledge, the first publication that reported on double precision accuracy on GPUs that natively only support single precision (at that time), with a significant speedup over double precision on the CPU. Chapter 4 and several sections in Chapter 5 are concerned with an update of this publication.

Our concept of the minimally invasive integration of hardware accelerators into FEAST (see Chapter 6) has been published in a series of three articles. The first one, in the *International Journal of Computational Science and Engineering* [87], presents the general concept, and its evaluation for the prototypical Poisson problem. The second one appeared in *Parallel Computing* in 2007 and extends the analysis to weak scalability and energy efficiency on a cluster of 160

GPUs [84]. Due to delays in the publication process, this paper finally appeared before the first one. The third paper in the series, again in the *International Journal of Computational Science and Engineering* [90], applies our concept to the acceleration of FEASTSOLID, an application built on top of FEAST for the simulation of large-scale solid mechanics problems (developed by Wobker [242]). These articles have been co-authored with Robert Strzodka, Hilmar Wobker, Jamaludin Mohd-Yusof, Patrick McCormick and other members of the FEAST group.

The author of this thesis also contributed significantly to another journal paper by the FEAST group, which emphasises the concepts of hardware-oriented numerics and compares the performance of FEAST on supercomputers and GPU-accelerated clusters. This article is accepted for publication in *Concurrency and Computation* [233]. Software design issues in heterogeneous high performance computing with accelerator hardware have been pursued in the HONEI project at TU Dortmund, the design approach and preliminary results have been published in *Computer Physics Communications* [236].

Our efficient implementation of cyclic reduction for the parallel solution of tridiagonal systems (cf. Section 5.4), co-developed with Robert Strzodka, has been written up for publication in the *IEEE Transactions on Parallel and Distributed Systems*, and recently got accepted [80].

The results from recent joint work with Dimitri Komatitsch, Gordon Erlebacher and David Michéa on accelerating a finite element seismic wave propagation simulation on a large cluster of 192 GPUs have been accepted for publication in the *Journal of Computational Physics* in April 2010 [136].

# **Conference Proceedings**

The early dissemination of intermediate results at international conferences, and the resulting discussions with expert practitioners in the field, is extremely important. Highlights during the pursuit of this thesis include:

The very first paper by the author of this thesis, presented at a small conference in Germany, has been to the best of our knowledge the first to achieve double precision accuracy on single precision GPUs by revisiting mixed precision iterative refinement methods from a performance perspective [82]. This work has gained quite some interest in the community, and as a consequence, we have been invited to present our work in a minisymposium held in conjunction with the renowned *ACM/IEEE Supercomputing conference* in November 2006.

The minimally invasive co-processor acceleration, applied to the solution of large-scale linearised elasticity problems, has been accepted as a poster presentation a year later [86].

A submission to the *International Conference on Supercomputing (ISC)* in 2008 reporting on hardware-oriented numerics as implemented in FEAST and applied to our approach to integrate GPU acceleration (co-authored by the entire FEAST group), has received the PRACE award <sup>6</sup> which recognises contributions of young researchers towards petascale computing.

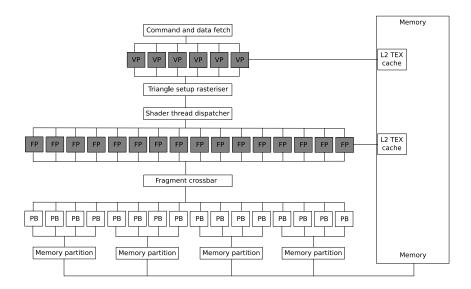

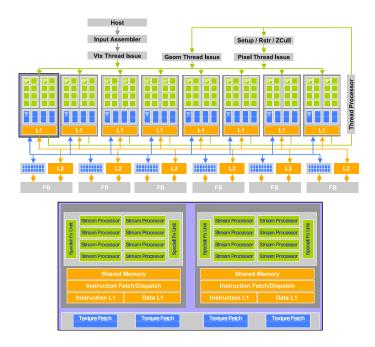

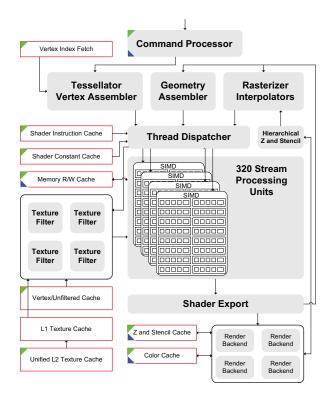

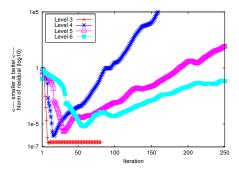

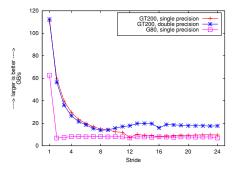

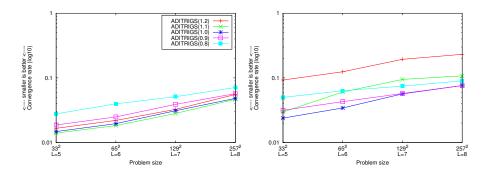

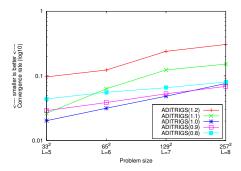

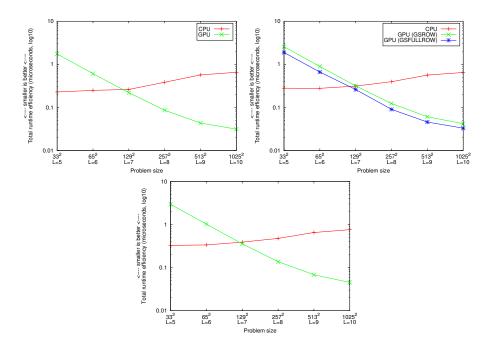

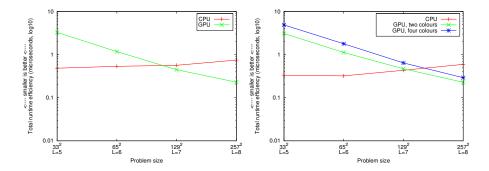

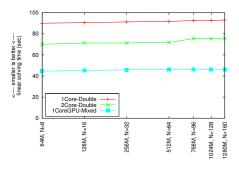

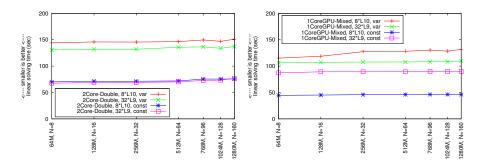

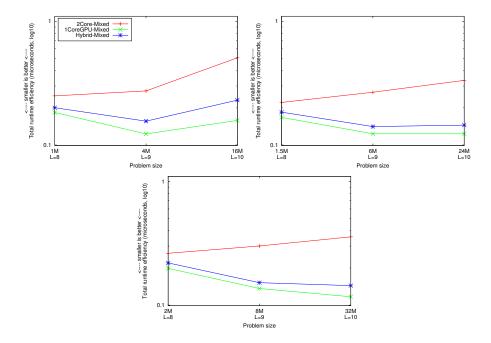

Our development of mixed precision schemes has been recognised by NVIDIA, and we have been able to experiment on early engineering samples of their first GPU architecture that supports double precision natively in hardware [79]. The results have been presented in an invited talk at their first NVISION conference on visual computing.