# IET Generation, Transmission & Distribution

# Special issue Call for Papers

Be Seen. Be Cited. Submit your work to a new IET special issue

"Emerging Applications of IoT and Cybersecurity for Electrical Power Systems"

Lead Guest: Editor Mohamed M. F. Darwish Guest Editors: Mahmoud Elsisi, Diaa-Eldin A. Mansour, Mostafa M. Fouda and Matti Lehtonen

**Read more**

#### DOI: 10.1049/gtd2.12605

## The Institution of Engineering and Technology WILEY

#### ORIGINAL RESEARCH

### An inertia-emulation-based cooperative control strategy and parameters design for multi-parallel energy storage system in islanded DC microgrids

Gang Lin<sup>1</sup> | Jiayan Liu<sup>1</sup> | Yang Zhou<sup>1</sup> | Yong Li<sup>2</sup> | Christian Rehtanz<sup>1</sup> | Shaoyang Wang<sup>2</sup> | Pengcheng Wang<sup>3</sup> | Wei Zuo<sup>4</sup>

<sup>1</sup>Institute of Energy Systems, Energy Efficiency and Energy Economics, TU Dortmund University, Dortmund, Germany

<sup>2</sup>College of Electrical and Information Engineering, Hunan University, Changsha, China

<sup>3</sup>College of Electrical Engineering, Zhejiang University, Hangzhou, China

<sup>4</sup>College of Electrical Engineering, University of Leeds, Leeds, UK

#### Correspondence

Gang Lin, Institute of Energy Systems, Energy Efficiency and Energy Economics, TU Dortmund University, Dortmund 44227, Germany, Email: 1287937851@qq.com

Yong Li, College of Electrical and Information Engineering, Hunan University, Changsha, China. Email: yongli@hnu.edu.cn

#### Funding information

China Scholarship Council, Grant/Award Number: 201906130196

#### **Abstract**

This paper proposes an inertia-emulation-based cooperative control strategy for the multi-parallel energy storage system (ESS) to meet the requirements of state-of-charge (SoC) balance, inertia enhancement and zero-steady-state voltage deviation. The inertia emulation loop (IEL) is constructed by analogy with DC motors to dampen voltage oscillation, while the secondary voltage recovery loop is derived from the circuit equivalence of an inductor to indicate the system stiffness. Moreover, to equalize SoCs of energy storage units (ESUs) dynamically, a SoC self-balance algorithm is developed. The redefined SoC mismatch degree and balance speed adjustment factor k are introduced into the droop resistance, adjusting the SoC self-balance rate and eliminating the SoC deviation among ESUs. The dynamic performance of the SoC self-balance algorithm is analyzed and the small signal model of the DC microgrid (DC-MG) with proposed strategy is established. Based on eigenvalue analysis and step response, the system stability is assessed, and the influence of control parameters on transient characteristics and stability margin is investigated. Considering power constraint, voltage deviation constraint and dynamic stability constraint, the optimal design method of k is given. Finally, simulation and experiment verify that the proposed control, without modifying hardware, performs better dynamic and static characteristics and can equalize SoC among ESUs in charge and discharge mode.

#### INTRODUCTION

In terms of seamless integration of renewable energy generation and multi-parallel energy storage systems (ESS) into industrial applications, such as electric vehicle (EV) charging stations and smart buildings, dc microgrid (DC-MG) is a promising architecture, due to its high power conversion efficiency, flexibility and reliability, and no concern on power angle stability [1, 2]. Interface converters replace conventional rotating machines and normally adopt droop control and dual loop control with response time in microseconds or milliseconds, and thus cannot provide sufficient damping and inertia for DC-MG. The inherent capacitor inertia is much smaller than rotating inertia,

making DC-MG an inertia-less system [3]. During the random variation of load and/or REG, DC voltage fluctuates dramatically, damaging sensitive loads and multi-parallel ESS [4]. Besides, the energy storage units (ESU) forming multiparallel ESS might be in inappropriate operation mode, such as over-charge/-discharge and state of charge (SoC) imbalance, degrading their lifespans [5]. Hence, the major issues in multi-parallel ESS of DC-MGs are to achieve SoC balance and improve the dynamic voltage stability, which will be solved simultaneously in this article.

Compared with connecting capacitors which bring extra power loss and are restrained by certain application scenarios with limited space, such as ship electric systems, inertia

This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

© 2022 The Authors. IET Generation, Transmission & Distribution published by John Wiley & Sons Ltd on behalf of The Institution of Engineering and Technology.

emulation is a creditable method to maintain the voltage stability. Virtual inertia control (VIC) and its improved control algorithm originally concentrate on AC systems to improve frequency regulation by simulating output characteristics of synchronous generators [3, 6], and only a few studies focus on the VIC application in DC systems to improve the voltage stability [7–12]. VIC for bidirectional grid-connected converter (BGC) is proposed in [7], and thus the DC-MG inertia is enhanced and the voltage fluctuation is restrained by the energy from the utility grid. In [8], virtual synchronous generator control damping dc voltage oscillation is presented, and its working mechanism in different modes is analysed thoroughly. In DC-MG lacking BGC, auxiliary power (i.e. inertia and damping power) alleviating voltage fluctuation is from ESU connecting to DC bus via bidirectional DC converter (Bi-C) [4, 9]. An inertia and damping control is proposed, making the external characteristic of converter consistent with the charge/discharge process of capacitor [8], and based on the DC machine model and its speed regulation theory, a virtual DC machine (VDCM) control is introduced in [4]. Still, the controller design is complicated, increasing the difficulty of its practical application. In [24], power-loop-free VDCM is proposed to eliminate the calculation of torques by using power measurements, reducing required resources for implementation. Different from the above methods realizing inertia emulation by analogy with machine or adding extra inertia loop, inertia response in [10] results from the fast droop-curve swing related to the voltage variation. However, damping improvement is ignored. Reference [11] proposes a VIC method, and a feedback analytical approach is presented to identify the motion of DC voltage intuitively and comprehend the stability principle deeply. In [23], an adaptive coordinated control scheme that can provide adaptive virtual inertia and virtual governor-gain support is proposed to enhance the stability of the networked AC/DC MGs while keeping power sharing among these MGs. The low-frequency oscillation mechanism in DC-MGs is revealed and the potential instability factors are identified in [25] to design a related improved loop. It is worth noting that the SoC balance issue, ignored in [7–11, 23–25], is considered in [12] where SoC is integrated into the droop coefficient of VDCM to enhance inertia and balance SoC simultaneously. VDCM in [12, 13, 24] possesses the same structure as that in [11], but lacks a fast-response inner voltage controller, degrading voltage tracking ability, even worse, bringing negative impacts for stability maybe.

To ensure the voltage stability of DC-MG, the voltage support ability of multi-parallel ESS should be fully utilized [14]. However, SoC imbalance might occur among battery cells or ESUs, reducing the overall performance of multi-parallel ESS. Most studies ignore the voltage support capabilities of ESS to improve system inertia and stability while balancing the SoC, which is another focus of this paper. For instance, a battery management system has been developed for the SoC balancing of battery cells connected in series inside ESU [15]. But, the SoC balancing of ESUs deserves attention to avoid unexpected hazards, for instance, over-heat and explosion. Hierarchical control is presented in [16] to equalize SoC at both cell level and ESU level by its modulation scheme for the duty cycle of switches.

Reference [17] adds SoC information into current deviation factor to modify current reference and balance SoC, degrading current regulation ability. The droop coefficient is adjusted by a proportional-integral (PI) controller according to SoC level to achieve SoC balance, but the extra controller complicates the parameter design [18]. The above methods make the control complex and increase their difficulty in practical application. An improved SOC balancing strategy based on low bandwidth communication is proposed in [26] where the SOC balancing efficiency is improved and the current deviation is removed by using the SOC slope-adjusting and current-shifting approaches simultaneously. Besides, SoC information can be incorporated into the droop coefficient in other forms, such as the difference between ESU SoC and the average SoC (SoC<sub>av</sub>) [5], the degree of SoC unbalance [12], and SoCn [19, 20], to redistribute power and remove SoC divergence. Solutions have been developed for SoC unbalance, but these methods have theoretical incompleteness, lacking parameter optimization design method considering various constraints for example. Reference [27] proposed a local-distributed and global-decentralized SoC balancing method for hybrid series-parallel ESS to achieve global SoC balancing and power sharing of ESUs. In [28], an adaptive control algorithm is proposed to balance the SOCs for a series-connected battery system using the current-SOC droop concept. Furthermore, the state-of-health status of battery cells is accounted in the SoC balancing method [29]. Few studies describe the association of the SoC balance and inertia enhancement, except [12], but lacking inner voltage controller leads to poor voltage tracking ability. Besides, the optimal selection method of balance speed adjustment factor, considering variable and stability constraints, is less proposed. Therefore, there is no suitable method to simultaneously solve the SoC imbalance and stability problems of multi-parallel ESS.

To address the aforementioned issues, focusing on the SoC self-balance among ESUs and system stability enhancement, this paper proposes an inertia emulation-based cooperative control strategy. The inertia emulation loop (IEL) is derived from the physical model of motors. Moreover, according to the real-time SoC information, SoC-integrated droop resistance is redefined as adaptive droop coefficient, and the SoC selfbalance algorithm can dynamically adjust delivered power to eliminate SoC divergence. Compared with integrator-based SoC balance methods, the proposed strategy has better extensibility because of its simpler parameter design and bandwidth coordination. Different from [11–13], the internal dual loop control structure ensures fast and accurate voltage tracking capability. The SVR loop is constructed based on the circuit equivalence of inductor, to reflect the system stiffness and expand the selecting range of k in the scenario of larger  $\Delta$ SoC. Control principle and implementation, stability analysis of each loop and parameter design considering various constraints are presented in detail. Simulation and hardware in loop (HIL) experiment verify the performance of the proposed control method.

Compared with previous studies that only pay attention to the series-connection structure, ignore the combination of SoC balance and IEL, do not deal with the contradiction between SoC balance speed and system stability, or lack parameter

optimization selection method, an inertia-emulation based cooperative control strategy is proposed in this paper to solve both the SoC imbalance and voltage deviation problems during steady-state operation, and the voltage stability problem caused by inertia-less in the transient process. Besides, the contradiction between SoC balancing speed and maintaining system stability is addressed. System stability and influences of parameters on dynamics are investigated by time-domain modelling and analysis. The major innovation and contributions of this work are

- A cooperative control strategy is proposed to balance the SoC of the multi-parallel ESS of DC-MGs. The defined SoC mismatch degree and balance speed adjustment factor k are incorporated into the redefined droop resistance by SoC selfbalance algorithm to balance SoC dynamically and adjust the balance rate, which is the main innovation different from previous research.

- The contradiction between SoC balancing speed and maintaining system stability is addressed by the reconstructed SoC-based droop resistance function, which is not considered in previous literatures.

- 3. The optimal design method of *k* is given considering variable constraints and dynamic stability constraint, ensuring SoC self-balance algorithm will not affect stability. This optimal design method has not been involved before.

- 4. IEL is proposed to enable multi-parallel ESS to provide virtual inertia to Bi-C, and to improve the voltage stability. Different from previous inertia control, this IEL is designed based on the detailed DC motor model, giving all the control parameters a clearer physical meaning. And the rated value of output voltage is added into the IEL, thus, the proposed IEL only acts in the transient process with a better control performance and would not affect the static characteristic (i.e. voltage regulation and power sharing).

- Based on the circuit equivalence of inductors, SVR is constructed to achieve zero steady-state voltage deviation by short-circuiting droop resistor and the system stiffness is improved, which is not involved in previous literatures.

#### 2 | PRINCIPLE OF IEL AND SOC SELF-BALANCE ALGORITHM

#### 2.1 | Circuits of Bi-C and DC motor

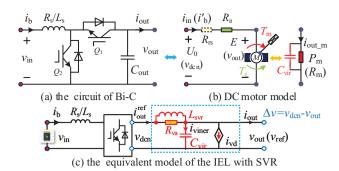

The two-port network of Bi-C is shown in Figure 1a. The front end is connected with ESU (battery usually) and the back end is linked to DC bus via DC cable.  $v_{\rm in}$  and  $v_{\rm out}$  are the input and output voltages of Bi-C;  $i_{\rm b}$  and  $i_{\rm out}$  are the input and output currents.  $L_{\rm s}$ ,  $R_{\rm s}$  and  $C_{\rm out}$  are the filter inductance, resistance, and output capacitor, respectively. The physical model of DC motor is shown in Figure 1b.  $U_0$  is the input voltage of motor and E is armature winding induced potential.  $R_{\rm a}$  is armature winding resistance and  $R_{\rm rs}$  is the speed regulating resistance. M is the mechanical inertia of DC motor, representing the role of rotor kinetic energy in the dynamic process.  $T_{\rm m}$  is the load torque and  $P_{\rm m}$  is the introduced electrical power to simulate the mechanical

**FIGURE 1** Mapping between Bi-C and DC motor, and *RLC* model for virtual inertia

TABLE 1 Analogy between DC motor/inductor and Bi-DC converter

| Physical meaning     | DC motor and Inductor         | RLC model of IEL         |

|----------------------|-------------------------------|--------------------------|

| Moment of inertia    | Rotor (M)                     | ESS (J <sub>vir</sub> )  |

| Damping source       | The friction $(D_{\rm damp})$ | $i_{\rm vd}~(D_{\rm d})$ |

| Stiffness            | $L_{ m svr}$                  | $i_{\rm svr}(k_{\rm s})$ |

| Droop characteristic | $R_{\rm a} + R_{\rm rs}$      | $R_{ m va}$              |

| Input voltage        | $U_0$                         | $v_{ m dcn}$             |

| Output voltage       | E                             | $v_{ m out}$             |

| Load                 | $T_{\rm m} (P_{\rm m})$       | $P_{ m out}$             |

| Input current        | $i_{ m in}$                   | $i$ ref out $(i'_b)$     |

power with respect to  $T_{\rm m}$ . At this time, an additional resistance  $R_{\rm m}$  and a virtual capacitor  $C_{\rm vir}$  storing inertia energy are added to achieve power balance. The circuit and power balance equations are in (1). The stored kinetic energy can effectively restrain voltage fluctuation caused by power imbalance. With M ( $C_{\rm vir}$ ) increasing, the rate of voltage change becomes smaller.

$$\begin{cases} E = U_0 - i_{\rm in} (R_{\rm a} + R_{\rm rs}) \text{ (a)} \\ P_{\rm c} - P_{\rm m} = \frac{\omega M}{C_{\rm T} \Psi} \frac{\mathrm{d}E}{\mathrm{d}t} \approx \frac{\omega_{\rm on} M}{C_{\rm T} \Psi} \frac{\mathrm{d}E}{\mathrm{d}t} = C_{\rm vir} \frac{\mathrm{d}E}{\mathrm{d}t} \text{ (b)} \end{cases}$$

(1)

From (1a), the DC motor can change its operation point and output power through speed regulation resistance  $R_{\rm rs}$  featuring (self-adaptive) droop characteristics, as shown in (2).

$$P_{\rm m} = E i_{\rm out\_m} = U_0^2 R_{\rm m} / (R_{\rm rs} + R_{\rm a} + R_{\rm m})^2$$

(2)

#### 2.2 | The design of IEL and SVR loop

Based on Figures 1a and 1b, the analogy between DC motor and Bi-C is in Table 1. On this basis, the IEL equation can be obtained as in (3) and (4) and its concept model is in Figure 1c. Its essence is systematic coordination of virtual capacitor, active damping and virtual resistance by exploring the auxiliary power in ESU properly to perform inertia and droop features.

$$i_{\rm b}^{\prime} - i_{\rm out} - i_{\rm vd} + i_{\rm svr} \approx \frac{\omega_{\rm on} M}{v_{\rm dcn} C_{\rm r} \Psi} \frac{\mathrm{d} v_{\rm ref}}{\mathrm{d} t} = \frac{1}{J_{\rm vir}} \frac{\mathrm{d} \left(v_{\rm ref} - v_{\rm dcn}\right)}{\mathrm{d} t} = i_{\rm viner} \quad (3)$$

$$\begin{cases} i_{b}' = i_{\text{out}}^{\text{ref}} = (v_{\text{dcn}} - v_{\text{out}} + \Delta v_{\text{svr}}) / R_{\text{va}} \text{ (a)} \\ i_{\text{vd}} = D_{\text{d}} (v_{\text{ref}} - v_{\text{out}}) \text{ (b)} \\ i_{\text{svr}} = \left[ k_{\text{s}} \int (v_{\text{dcn}} - v_{\text{out}}) dt \right] / R_{\text{va}} = \Delta v_{\text{svr}} / R_{\text{va}} \text{ (c)} \end{cases}$$

$$(4)$$

where  $v_{\rm dcn}$  is the rated value of  $v_{\rm out}$ .  $i_{\rm b}$  is actually the output reference  $i_{ref out}$ , which mainly includes  $i_{vd}$  (the virtual damping current),  $i_{\text{viner}}$  (the virtual inertia current),  $i_{\text{syr}}$  (the virtual inductor current), and  $i_{out}$ . The physical significance of  $i'_{b}$  is to represent energy supply and mimic  $i_{in}$ .  $v_{ref}$  is the virtual internal potential emulating E.  $R_{\rm va}$  is the virtual droop resistance in series on the Bi-C output side, making the Bi-C present droop feature. Consequently, iref out is obtained by the droop feature, as shown in (4a).  $J_{\text{vir}}$  and  $D_{\text{d}}$  are the introduced virtual inertia and damping coefficient, respectively. The introduced Jvir can be equivalent to the virtual (static) rotor, virtual capacitor  $C_{\text{vir}}$ actually, of Bi-C, mitigating voltage oscillation by supplying or absorbing power mismatch. Damping current  $i_{vd}$  is added to prevent voltage from deviating its rated value; thus, it is defined in proportional to the voltage deviation as shown in (4b).  $i_{vd}$  is provided till the voltage returns to its reference value.

Based on the circuit equivalence that inductors behave as short circuits at a long-time limit while open circuits at a short-time limit, virtual-inductor-based SVR is developed as shown in Figure 1c.  $L_{\rm svr}$  refers to the virtual inductor. The control law is 4(c) and  $k_{\rm s}$  is the stiffness coefficient, revealing the voltage recovery speed. At a long-time limit, the virtual inductor short-circuits  $R_{\rm va}$  and  $i_{\rm out}$  are transferred from  $R_{\rm va}$  to  $L_{\rm svr}$ , thus the voltage deviation  $\Delta v$  is eliminated. The control diagram is shown in Figure 2a.

It can be observed from Table 1 that the inertia and damping power of Bi-C originate from ESS instead of the rotational kinetic energy.  $i_{\rm viner}$  will be produced, when the voltage oscillates, to provide inertia to suppress voltage fluctuation, and more inertia current will be produced if oscillation frequency increases. Note that the oscillation frequency declines as  $J_{\rm vir}$  increases in the scenario requiring the same inertia current.  $i_{\rm vd}$  is generated when voltage deviates from its reference value, indicating voltage deviation is dependent on  $D_{\rm d}$ . In order to attain better performance, larger  $D_{\rm d}$ , leading to smaller voltage deviation, is preferred. The proposed strategy enables Bi-C to have inertia and damping features, and (self-adaptive) droop characteristics. Its detailed control diagram is in Figure 2a.

#### 2.3 | Principle of SoC self-balance algorithm

In order to promote SoC equalization, multi-parallel ESS should operate in the manner that the ESS with higher SoC should release more power in discharge mode and absorb less power in charge mode than the one with lower SoC, as illustrated in Table 2. Thus, the  $\Delta SoC_{ij}$  ( $\Delta SoC_{ij} = SoC_i - SoC_j$ ) would

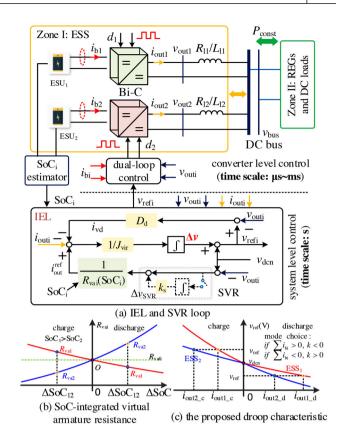

FIGURE 2 The diagram of DC-MG with the proposed control strategy

**TABLE 2** Design principle of droop resistance

| Mode             | RoCoV    | Action of ESS     | Droop resistance |

|------------------|----------|-------------------|------------------|

| Charging mode    | Negative | Reduce input ↓    | Increase ↑       |

|                  | Positive | Increase input ↑  | Reduce ↓         |

| Discharging mode | Negative | Increase output ↑ | Reduce ↓         |

|                  | Positive | Reduce output ↓   | Increase ↑       |

|                  |          |                   |                  |

RoCoV, rate of change of voltage.

be removed, avoiding uneven use and expanding their lifespan. Subscripts 'i' and 'j' are the ESU identifier index.

Learning from the speed regulation of DC motor, a SoC-integrated droop resistance  $R_{\rm vai}({\rm SoC_i})$  is redefined in the SoC self-balance algorithm, as shown in (5). Thus, power would be redistributed to balance SoC in charge and discharge modes.  $R_{\rm va0}$  is the initial value of  $R_{\rm vai}$  and is designed based on traditional droop methods [17]. k is the SoC equalization speed adjustment factor and selected to be negative in discharge mode and positive in charge mode, affecting the SoC balance speed. It is worth noticing that  $\lambda_i$  is a time-varying parameter indicating the SoC mismatch degree among SoC<sub>i</sub> and the SoC<sub>av</sub>, and also affects the SoC balance speed according to the time-varying SoC<sub>i</sub>, which is a novel contribution of this paper. It can be observed from (5) that  $R_{\rm vai}$  will return to  $R_{\rm va0}$  and power distribution will become equal, as  $\lambda_i$  gradually converges to 0. Note that k and  $\lambda_i$  affect the balance speed as exponent forms. The

droop control is shown in (6)

$$\begin{cases} R_{\text{vai}} = R_{\text{va0}} \text{SoC}_{i}^{-k\lambda_{i}}, & i = 1, 2, ..., n \\ \lambda_{i} = \text{SoC}_{i} - \text{SoC}_{\text{av}}, & \text{SoC}_{\text{av}} = \sum_{i=1}^{n} \text{SoC}_{i} / n \end{cases}$$

(5)

$$v_{\text{refi}} = v_{\text{dcn}} - R_{\text{vai}} i_{\text{outi}} \tag{6}$$

## 3 | DIAGRAM OF DC-MG WITH PROPOSED STRATEGY

Based on (3)–(6), the diagram of DC-MG with the proposed strategy is in Figure 2, including IEL and SVR part, SoC self-balance algorithm and dual loop control. A benchmark DC-MG composed of renewable energy generations, constant power load (CPL) and multi-parallel ESS is considered.

IEL and SVR link: The IEL consists of virtual inertia loop and damping loop, which enable Bi-C to compensate power mismatch by using the energy in ESS, improving the inertia of DC-MG and restraining the voltage fluctuation. The virtual inductor of the SVR loop acts as a short circuit of  $R_{\rm va}$  at a steady state, and  $i_{\rm out}$  is transmitted through the virtual inductor instead of  $R_{\rm va}$ . Hence,  $\Delta v$  is eliminated. SVR loop is activated selectively, which will be explained in Section 5.

SoC self-balance algorithm: SoC evaluator calculates the SoC<sub>i</sub>, according to the coulomb counting method, as shown in (7).  $C_{\rm e}$  is the capacity of ESU,  $d_{\rm i}$  is the duty cycle. SoC should be within the constraint range in (8) to ensure the service life. SoC<sub>min</sub> and SoC<sub>max</sub> are the minimum and maximum values, respectively. Then a central controller is required for SoC<sub>av</sub>. Each ESU calculates their  $R_{\rm vai}$  according to (5), regulating their delivered power according to the SoC<sub>i</sub> to achieve SoC balance.

$$SoC_{i} = SoC_{i, t=0} - \frac{1}{C_{e}} \int i_{bi} dt = SoC_{i, t=0} - \frac{1}{C_{e}} \int \frac{i_{outi}}{1 - d_{i}} dt$$

$$SoC_{min} \le SoC_i \le SoC_{max}$$

(8)

For the sake of simple analysis, taking the multi-parallel ESS composed of two ESUs as an example, the relation between  $R_{\rm vai}$  and  $\Delta {\rm SoC_{ij}}$ , and the droop characteristic are in Figures 2b and 2c, respectively. In the discharge mode with k < 0, ESU<sub>1</sub> with higher  ${\rm SoC_1}$  would supply more power at  $i_{\rm out1\_d}$  than ESU<sub>2</sub> with lower  ${\rm SoC_2}$  does at  $i_{\rm out2\_d}$  because of  $R_{\rm va1} < R_{\rm va2}$ . This implies that the SoC values of each ESU will move closer to each other to eliminate  $\Delta {\rm SoC_{12}}$  till  $\lambda_i = 0$ . Then, all ESUs would charge or discharge at the same rate, maintaining  $\lambda_i = 0$ . Consequently, the SoC self-balance algorithm equalizes the SoC gradually and can perform well in SoC-unbalanced and SoC-balanced scenarios.

*Dual loop control*: Dual loop control consists of voltage loop tracking  $v_{\text{ref}}$  accurately and current loop controlling the voltage indirectly, improving the control performance.

From Figure 2, the IEL and SoC self-balance algorithm are at the system level because the droop feature is from the redefined  $R_{\rm va}$ . Therefore, the bandwidth of each loop can be coordinated better and easier, enhancing the voltage tracking ability. The time scale of system level control is second, while the time scale of converter level control is microsecond or millisecond. SoC<sub>i</sub> need not be updated fast and its update cycle is 0.01 s, due to its slow variation. The impact of communication delay (microseconds usually) is also ignored, because it is much smaller than the inertia emulation part [21].

Normally, the resistance of DC cable is very small in DC-MG; thus, the voltage droop across transmission cable can be ignored as (9) [20]. Consequently, the power sharing relation among ESUs with the same capacities is in (10).

$$v_{\text{out1}} \approx v_{\text{out2}} \approx ... \approx v_{\text{outn}}$$

(9)

$$i_{\text{out1}}: i_{\text{out2}}: \dots: i_{\text{outn}} \approx i_{\text{b1}}: i_{\text{b2}}: \dots: i_{\text{bn}}$$

$$\approx \text{SoC}_1^{k\lambda_1}: \text{SoC}_2^{k\lambda_2}: \dots: \text{SoC}_n^{k\lambda_n}$$

(10)

The above analysis is for ESUs with the same capacity. When the ESU capacities differ significantly,  $R_{\rm va0}$  is chosen according to their capacity ratio, ensuring that the charge and discharge powers can be allocated reasonably. Thus, this SoC self-balance algorithm is also suitable for ESUs with different capacities.

## 4 | DYNAMIC PERFORMANCE AND STABILITY ANALYSIS

Taking multi-parallel ESS with two ESUs as an example, SoC balance speed regulation, stability analysis of SoC self-balance algorithm and small-signal stability analysis of IEL are presented.

#### 4.1 | SoC balance speed adjustment

$$SoC_{i} = SoC_{i, t=0} - \frac{i_{load}}{C_{c}} \int SoC_{i}^{k\lambda_{i}} / \sum_{i=1}^{n} SoC_{i}^{k\lambda_{i}} dt$$

(11)

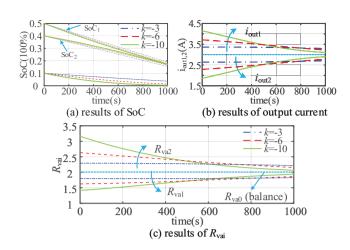

Combining (7) and (10), it yields (11). Selecting  $C_{\rm e}=3$  Ah,  $i_{\rm load}=6$  A,  ${\rm SoC}_{1,\,t=0}=50\%$ ,  ${\rm SoC}_{2,\,t=0}=40\%$  and  $R_{\rm va0}=2$ , the numeric solution of (11) in discharge mode is obtained as in Figure 3a. The delivered power and  $R_{\rm vai}$  are shown in Figures 3b and 3c. The related data is in Table 3 when t=800 s. It is shown that, under the same  $\Delta{\rm SoC}_{12}$ , a larger k would enlarge the differences of  $R_{\rm vai}$  and  $i_{\rm outi}$ , balancing SoC in a shorter time. At t=800 s,  $\Delta{\rm SoC}_{12}$  is 0.9%, 2.360% and 4.812% when k is -10, -6 and -3, respectively. From Figures 3b and 3c, the delivered power is inversely proportional to  $R_{\rm vai}$ .  $R_{\rm vai}$  of ESU<sub>1</sub> with higher SoC would be smaller to release more energy. As a result,  ${\rm SoC}_1$  and  ${\rm SoC}_2$  balance dynamically, then  $R_{\rm vai}$  return to  $R_{\rm vai}$ .

FIGURE 3 SoC balance speed regulation with different k

**TABLE 3** Numeric solution of SoC balance regulation when t = 800 s

| K   | $\Delta SoC_{12, t = 800}$ | $R_{\mathrm{va1}}$ | R <sub>va2</sub> | $i_{ m out1}$ | $i_{ m out2}$ |

|-----|----------------------------|--------------------|------------------|---------------|---------------|

| -10 | 0.900%                     | 1.868              | 2.146            | 3.208         | 2.792         |

| -6  | 2.360%                     | 1.808              | 2.229            | 3.313         | 2.687         |

| -3  | 4.812%                     | 1.811              | 2.243            | 3.320         | 2.680         |

## 4.2 | Stability analysis of the SoC self-balance algorithm

The stability of the SoC self-balance algorithm is evaluated by small signal analysis. Since the bandwidth of dual loop control is much higher than the SoC self-balance algorithm, a unity gain block represents the closed-loop gain of dual loop control. Perturbing (6), there is

$$\frac{-\Delta v_{\text{outi}}}{v_{\text{den}} - v_{\text{outi}}} = \frac{-k_{\text{dei}}}{i_{\text{outi}}} \Delta \text{SoC}_{i} + \frac{\Delta i_{\text{outi}}}{i_{\text{outi}}}, \quad i = 1, 2$$

(12)

$$k_{\text{dc1}} = ki_{\text{out1}} \left[ (\text{SoC}_1 - \text{SoC}_2) / \text{SoC}_1 + \ln(\text{SoC}_1) \right]$$

(13a)

$$k_{dc2} = ki_{out2} \left[ (SoC_2 - SoC_1) / SoC_2 + ln (SoC_2) \right]$$

(13b)

Linearizing (7), it yields (14).

$$\Delta SoC_{i} = \frac{\Delta i_{bi}}{sC_{e}} = -\frac{v_{outi}}{sv_{bi}C_{e}} \Delta i_{outi} = -\frac{\Delta i_{outi}}{sC'_{e}}$$

(14)

Combining (11) and (14), (15) and (16) can be obtained. For zone II, the simplified model is shown in (17). Based on KCL, the power balance equation is derived in (18).

$$\Delta i_{\text{out1}} = -2si_{\text{out1}}C'_{\text{e}}\Delta v_{\text{out1}} / \left[ (v_{\text{dcn}} - v_{\text{out1}}) \left( 2sC'_{\text{e}} + k_{\text{dc1}} \right) \right]$$

(15)

**TABLE 4** System parameters of the studied DC-MG

|                     | Items                                       | Value                       |

|---------------------|---------------------------------------------|-----------------------------|

| Zone I              | Input voltage $v_{\rm s}$                   | 100 V                       |

|                     | Input filter inductor $L_{\rm s}/R_{\rm s}$ | 5 mH/0.01 $\Omega$          |

|                     | Capacitance $C_{\mathrm{out}}$              | $3000  \mu \text{F}$        |

|                     | Line impedance $R_{\rm li}/L_{\rm li}$      | $0.01~\Omega/0.1~\text{mH}$ |

|                     | Initial value of $R_{\rm vai}/R_{\rm va0}$  | 2 Ω                         |

|                     | Sample frequency                            | 10 kHz                      |

| Zone II             | Bus voltage rating $v_{\rm dcn}$            | 300 V                       |

|                     | Net power $P_{\text{const}}(R)$             | 2900 W                      |

|                     | Equivalent load $R_{\rm const}$             | 30 Ω                        |

| Variable limitation | $\Delta v_{ m out\_max}$                    | 10 V                        |

|                     | $\Delta i_{ m outi\_max}$                   | 5 A                         |

|                     | $\Delta i_{ m bi\_max}$                     | 14 A                        |

$$\Delta i_{\text{out2}} = -2si_{\text{out2}}C'_{\text{e}}\Delta v_{\text{out2}} / \left[ (v_{\text{dcn}} - v_{\text{out2}}) \left( 2sC'_{\text{e}} + k_{\text{dc2}} \right) \right]$$

(16)

$$\begin{cases} i_{\text{load}} = v_{\text{bus}} / R_{\text{load}}, \text{ discharge mode } (a) \\ i_{\text{load}} = P_{\text{const}} / v_{\text{bus}}, \text{ charge mode } (b) \end{cases}$$

(17)

$$\sum_{i=1}^{n} \Delta i_{\text{outi}} = \Delta i_{\text{load}}$$

(18)

The characteristic equation can be derived from (15) to (18).

$$As^2 + Bs + C = 0 \tag{19}$$

$$\begin{cases} A = 4 \cdot C_{e}^{'2} \cdot (i_{\text{out1}} + i_{\text{out2}} + I_{\text{det}}) \\ B = 2 \cdot C_{e}^{'} \cdot (i_{\text{out1}} k_{\text{dc2}} + i_{\text{out2}} k_{\text{dc1}} + I_{\text{det}} (k_{\text{dc1}} + k_{\text{dc2}})) \end{cases}$$

$$C = k_{\text{dc1}} \cdot k_{\text{dc2}} \cdot I_{\text{det}}$$

$$I_{\text{det}} = (v_{\text{dcn}} - v_{\text{outi}}) / R_{\text{load}} \quad \text{discharge mode}$$

$$I_{\text{det}} = P_{\text{const}} (v_{\text{dcn}} - v_{\text{outi}}) / v_{\text{bus}}^{2} \text{ charge mode}$$

$$(20)$$

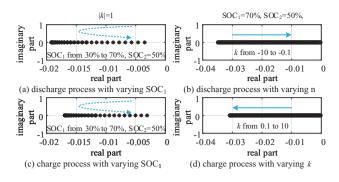

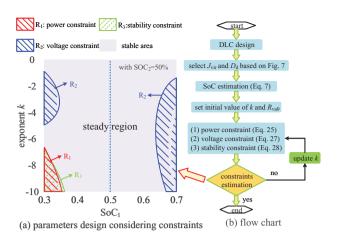

From (19), the dominant poles of SoC self-balance algorithm with different SoC and exponent k in charge and discharge modes are presented by using the parameters in Table 4, as shown in Figure 4. Usually, the SoC self-balance algorithm is an overdamped system; thus, only one dominant pole is left.

Figures 4a and 4c show the influences of  $SoC_1$  varying from 0.3 to 0.7 with  $SoC_2 = 50\%$  and |k| = 1 in discharge and charge modes. The increasing of  $SoC_1$  leads to the pole moving away from the imaginary axis first, and then towards the imaginary axis, which indicates that the stability is first improved and then weakened. When the SoC of two ESUs is close, the stability is approximately the strongest. Figures 4b and 4d show the influences of |k| varying from 0.1 to 10 in discharge and charge modes. With the increase of |k|, the pole moves away from

FIGURE 4 The dominant pole distribution of SoC self-balance algorithm

FIGURE 5 Small signal model of DC-MG with the proposed IEL

the imaginary axis, improving the stability, because a larger |k| makes SoC balance faster. But the current difference between ESUs is also greater and ESU<sub>1</sub> undertakes most of the load and is closer to its critical state; therefore, an upper limit of |k| is necessary and introduced later. In Figure 4, the pole is always on the left half plane, so stability of SoC self-balance algorithm is guaranteed.

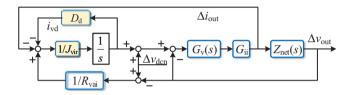

#### 4.3 | Small signal stability analysis of IEL

Ignoring the power loss, (21) is derived from power balance.

$$V_{s}\Delta i_{s} = (I_{\text{out}} + s \times 2 \times C_{\text{out}} V_{\text{out}}) \Delta v_{\text{out}} + V_{\text{out}} \Delta i_{\text{out}}$$

(21)

Therefore, the relation between  $\Delta i_{\rm out}$  and  $\Delta i_{\rm b}$  can be obtained when virtual-inductor-based SVR is not connected.

$$G_{ii} = \Delta i_{out} / \Delta i_{b} = V_{s} / V_{out}$$

(22)

The closed-loop gain of current loop is equivalent to unity gain block. Based on (21), (22) and Figure 2a, the small-signal model of IEL is established in Figure 5.  $G_{\rm v}({\rm s})$  is the voltage PI regulator.  $Z_{\rm net}(s)$  is the small-signal impedance of Zone II and lines. The relation between  $\Delta v_{\rm out}$  and  $\Delta i_{\rm out}$  is in (23) and its physical significance is to reflect the dynamic response of  $v_{\rm out}$  when  $i_{\rm out}$  changes suddenly. The transfer function of  $\Delta v_{\rm out}$  and  $\Delta v_{\rm den}$  is in (24), reflecting the voltage tracking ability.

$$TF_{i\_id} = \frac{\Delta v_{\text{out}}}{\Delta i_{\text{out}}} = \frac{-G_{\text{v}} \times G_{\text{ii}} \times Z_{\text{net}}}{sJ_{\text{vir}} + D_{\text{damp}} + G_{\text{v}} \times G_{\text{ii}} \times Z_{\text{net}} (1/R_{\text{vai}} + sJ_{\text{vir}})}$$

FIGURE 6 Dynamic stability analysis of DC-MG with the IEL

$$TF_{v_{\text{id}}} = \frac{\Delta v_{\text{out}}}{\Delta v_{\text{dcn}}}$$

$$= \frac{(1/R_{\text{vai}} + sJ_{\text{vir}}) \times G_{\text{v}} \times G_{\text{ii}} \times Z_{\text{net}}}{sJ_{\text{vir}} (1 + G_{\text{v}}G_{\text{ii}}Z_{\text{net}}) + D_{\text{damp}} + G_{\text{v}} \times G_{\text{ii}} + G_{\text{v}}G_{\text{ii}} \times Z_{\text{net}}/R_{\text{vai}}}$$

(24)

The pole distribution of  $TF_{i id}(s)$  and step response of  $TF_{\text{v id}}(s)$ , with varying  $D_{\text{d}}$  and  $J_{\text{vir}}$ , are presented, as in Figure 6. From Figures 6a and 6b, remarkably, the DC-MG with IEL can be simplified to a third-order system approximately, including a negative real root (representing the inertia component) and a pair of negative conjugate complex roots (representing lowfrequency oscillation mode). In Figure 6a, with  $D_d$  increasing from 2 to 7, the poles of oscillation mode move to real axis, and the damping increases first and then decreases. At about  $D_{\rm d}$  = 4, the damping is maximum. Besides, the time constant  $T_{\rm iner}$  of the inertia component decreases with  $D_{\rm d}$  increasing, indicating that system inertia is weakened. The opposite movement trend of poles, with  $J_{vir}$  increasing, can be observed in Figure 6b. The damping of oscillation mode is first increased and then decreased, and the poles move away from real axis and oscillation frequency increases. The poles are always on the left half plane, confirming the stability of inertia emulation part.

In Figure 6c, with the increase of  $J_{vir}$  and  $D_d$ , the oscillation damping first increases and then decreases, which is consistent with Figures 6a and 6b.

#### 5 | PARAMETERS DESIGN GUIDANCE

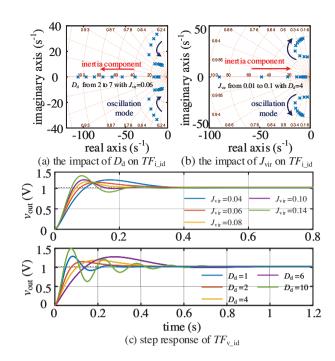

In the SoC self-balance algorithm, the exponent k changes the SoC balance speed by adjusting the power allocation. In this

FIGURE 7 Different constraints for exponent k

process,  $R_{\rm vai}$  will be dynamically adjusted according to k and SoC, which would affect  $i_{\rm outi}$ ,  $v_{\rm outi}$  and transient performance. Therefore, power constraint, voltage constraint and dynamic stability constraint should be considered while selecting k. Two ESUs in discharge mode are taken as an example. SoC<sub>1</sub> changes from 30% to 70% and |k| changes from 0 to 10 with SoC<sub>2</sub> = 50%.

#### 5.1 | Power constraint

The sharing of  $P_{\rm const}$  can be derived from (10), as shown in (25), which is not only related to k but also related to the  $\Delta {\rm SoC_{ij}}$  of ESU. The output/injected current of Bi-C and ESU should not exceed their maximum value, that is,  $i_{\rm outi\ max}$  and  $i_{\rm bi\ max}$ .

$$\begin{cases} i_{\text{outi}} = \left( \text{SoC}_{i}^{k\lambda_{i}} / \sum_{i=1}^{n} \text{SoC}_{i}^{k\lambda_{i}} \right) i_{\text{load}} \leq i_{\text{outi\_max}} \text{ (a)} \\ i_{\text{bi}} = \left( \text{SoC}_{i}^{k\lambda_{i}} / \sum_{i=1}^{n} \text{SoC}_{i}^{k\lambda_{i}} \right) \frac{v_{\text{outi}}}{v_{\text{si}}} i_{\text{load}} \leq i_{\text{bi\_max}} \text{ (b)} \end{cases}$$

$$(25)$$

Figure 7a shows how the power sharing would be affected by  $SoC_i$  and k. The larger k, with the same  $\Delta SoC_{ii}$ , enlarges the

power allocation difference between ESUs, which might cause the ESU power to exceed its maximum though balancing SoC faster. The relation between  $i_{\text{outi}}$  and k, when  $\Delta \text{SoC}_{12} = -20\%$ , is in Figure 7b. It can be found that the power released by ESU<sub>2</sub> exceeds its acceptable power rating when k exceeds  $k_{\text{i\_limit}} \approx 6.5$ , degrading its lifespan. Power constraint is an upper limit to k.

#### 5.2 | Voltage deviation constraint

The maximum voltage deviation  $\Delta v_{\rm outi}$  caused by droop feature is another constraint of k.  $R_{\rm va0}=2$  can be obtained from (26). Combining (10) and (25), the quadratic equation of  $\Delta v_{\rm outi}$  can be derived from (4a), as shown in (27).  $\Delta v_{\rm outi}$  can be acquired by solving (27), as shown in (28). The other solution of (27) is rejected because it exceeds  $v_{\rm dcn}$ . From (28),  $\Delta v_{\rm outi}$  is affected by  ${\rm SoC_i}$ , k and  $P_{\rm const}$ , and their relationship is shown in Figure 7c. When  $|\Delta {\rm SoC_{12}}|$  is large, there would be a set of k making  $v_{\rm outi}$  exceed its constraint value. Figure 7d shows the relation between  $\Delta v_{\rm outi}$  and k, when  $\Delta {\rm SoC_{12}}=-20\%$ .  $\Delta v_{\rm outi}$  would locate in the unsafe region when  $k \in [k_{\rm v\_lim1}, k_{\rm v\_lim2}]$ , degrading power quality. Therefore, Equation (28) provides a regional limit for k.

$$R_{\text{va0}} = \Delta v_{\text{out max}} / \Delta i_{\text{out max}} \tag{26}$$

$$\Delta v_{\text{outi}} = -\frac{R_{\text{va0}}i_{\text{load}}}{\sum_{i=1}^{n} \text{SoC}_{i}^{k\lambda_{i}}} = -\frac{R_{\text{va0}}}{\sum_{i=1}^{n} \text{SoC}_{i}^{k\lambda_{i}}} \frac{P_{\text{const}}}{v_{\text{outi}} + \Delta v_{\text{outi}}}$$

(27)

$$|\Delta v_{\text{outi}}| = \left| \left( -v_{\text{dcn}} + \sqrt{v_{\text{dcn}}^2 - 4 \frac{R_{\text{va0}} P_{\text{const}}}{\sum_{i=1}^{n} \text{SoC}_{i}^{k \lambda_{i}}}} \right) / 2 \right| \le \Delta v_{\text{out\_max}}$$

(28)

#### 5.3 Dynamic stability constraint

As mentioned before,  $R_{\rm vai}$  is regarded as a virtual impedance connected in series on the Bi-C output side, affecting the system damping  $\xi$ . According to (24), the influence of  $R_{\rm vai}$  on the system dynamic characteristics is shown in Figure 7e. Note that  $\xi$  first increases and then decreases with  $R_{\rm vai}$  increasing. To ensure a good dynamic response,  $\xi$  should not be less than 0.707, thus from Figure 7e,  $R_{\rm vai}$  should not be less than  $R_{\rm va\_lim} = 1.25$ . Considering (6), the dynamic stability constraint is in (29).

$$R_{\text{vai}} = R_{\text{va0}} \text{SoC}_{\text{i}}^{-k\lambda_{\text{i}}} \ge R_{\text{va\_lim}}$$

(29)

Figure 7f shows the influences of SoC and k on  $R_{\rm vai}$ . The difference in  $R_{\rm vai}$  becomes larger with the increase of k, resulting in larger power allocation difference and accelerating the SoC balance speed. However, the ESU releasing more power is with a smaller  $R_{\rm vai}$ , degrading the system damping and deteriorating dynamic characteristic. Hence, the dynamic stability constraint provides an upper limit for k.

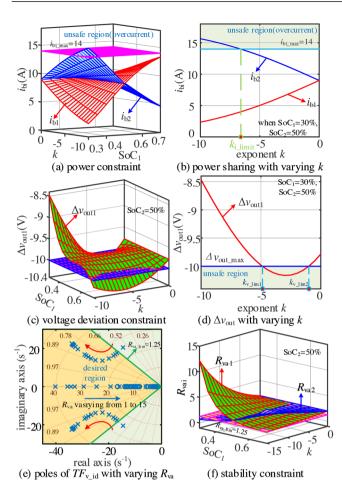

FIGURE 8 Constraint estimation and parameter optimization flow chart

Considering these three constraints, constraints estimation is performed, as shown in Figure 8a. Lower limit of |k| is not required. The power is equally distributed among ESUs when  $R_{\rm vai}=R_{\rm va0}$  and k=0. From Figure 7f, the dynamic stability is ensured because  $R_{\rm va0}$  is within the acceptable range. Power and voltage deviation constraints would also be obeyed, when ESUs with  $R_{\rm vai}=R_{\rm va0}$  supply power within rated range. Hence, the above three constraints are upper and region limitations.

The flow of control parameter design and optimized selection range is shown in Figure 8b. The specific process is as follows:

- 1. PI controllers of dual-loop control are designed according to the requirements of phase margin and amplitude margin [13].

- 2. As shown in Figure 6,  $J_{\rm vir}$  and  $D_{\rm d}$  are selected based on the standards of dynamic performance ( $\xi$  and  $T_{\rm iner}$ ). Note that the impact of oscillation mode should not be ignored.

- 3. Set  $R_{va0}$  from Equation (26); choose the initial value of k according to the SoC balance speed (Figure 3).

- 4. Draw Figure 8a based on Equations (25), (28) and (29) for constraint estimation. If these constraints are met, it indicates that the selected *k* is reasonable, if not, an appropriate *k* should be chosen according to Figure 8a.

## 6 | SIMULATION AND EXPERIMENT VERIFICATION

Simulation and dSPACE-based HIL experiment is conducted to validate the effectiveness of the proposed control strategy. The islanded DC-MG system similar to Figure 2 is tested and  $P_{\rm const}$  is changed suddenly to imitate the power disturbance. The parameters are in Tables 4 and 5.

#### 6.1 | Simulation result

In order to verify the inertia effect and voltage regulation ability of the proposed strategy, it is compared with the droop control

**TABLE 5** Control parameters of different control

| Control Strategy       | Item                                       | Value      |

|------------------------|--------------------------------------------|------------|

| Dual loop control      | Droop coefficient R <sub>a</sub>           | 2 Ω        |

|                        | Voltage loop $k_{\rm vp}$ + $k_{\rm vi}/s$ | 1 + 10/s   |

|                        | Current loop $k_{ip} + k_{ii}/s$           | 5 + 1/s    |

| VDCM control           | Droop coefficient $R_a$                    | 2 Ω        |

|                        | Virtual armature resistance                | 1.2 Ω      |

|                        | Voltage loop $k_{\rm vp} + k_{\rm vi}/s$   | 0.1 + 50/s |

|                        | Virtual inertia $J_{ m vir}$               | 2 F        |

|                        | Virtual damping $D_{\rm damp}$             | 10         |

| Inertia emulation loop | Virtual inertia $J_{ m vir}$               | 0.06       |

|                        | Virtual damping $D_{\rm d}$                | 4          |

|                        | droop resistance $R_{\rm va0}$             | 2 Ω        |

|                        | Voltage loop $k_{\rm vp} + k_{\rm vi}/s$   | 0.1 + 50/s |

|                        | SVR &s                                     | 1          |

|                        | $SoC_{1, t=0} / SoC_{2, t=0}$              | 80%/70%    |

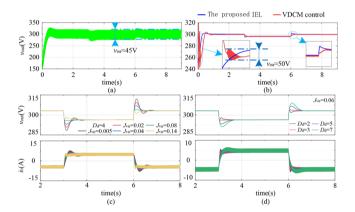

FIGURE 9 Comparison of different control strategies

FIGURE 10 The influence of k on SoC balance speed

and VDCM control [12, 13]. The results are shown in Figures 9 and 10. The voltage oscillates severely under droop control, indicating that DC-MG lacks damping and inertia.

It can be seen from Figure 9b that the dynamic performance is improved significantly when IEL or VDCM works, and  $v_{\rm out}$  can move to steady state without oscillation. Since the proposed

FIGURE 11 The HIL experimental platform

IEL is in the system level control, it does not destroy bandwidth coordination, and thus can eliminate voltage oscillation in the initial stage. The transient behaviour is improved and the voltage-tracking ability at the startup phase is enhanced, compared with droop control and previous VDCM control. The influences of  $J_{\rm vir}$  and  $D_{\rm d}$  are shown in Figures 9c and 9d, respectively. When  $J_{\rm vir}$  or  $D_{\rm d}$  selects a small value,  $v_{\rm out}$  would achieve stability after a short period of oscillation. The oscillation will be better suppressed and a good transient behaviour would be acquired when larger  $J_{\rm vir}$  or  $D_{\rm d}$  is chosen. The damping of oscillation mode would decrease with the increase of  $J_{\rm vir}$  or  $D_{\rm d}$ , which is consistent with Figure 6. Therefore,  $\xi$  and  $T_{\rm iner}$  should be considered together when selecting  $J_{\rm vir}$  and  $D_{\rm d}$ .

$P_{\rm const}$  and the operation mode are changed every 3 s. When  $t \in [0, 0.5 \, {\rm s}]$  (the startup stage), the SoC balance algorithm does not work. After  $t=0.5 \, {\rm s}$ , the SoC self-balance algorithm is activated. The simulation results are in Figure 10. From Figures 10b and 10c,  $R_{\rm va1}$  of ESU<sub>1</sub> with a larger SoC is smaller in discharge mode, and thus the output current is larger. In the charge mode,  $R_{\rm va1}$  is larger and the injected current is smaller. As a result,  $\Delta {\rm SoC}_{12}$  is decreased to 0. It can be concluded from Figure 10d that, after a same time period, the final  $\Delta {\rm SoC}_{12}$  with a higher |k| becomes smaller, indicating that the SoC equalization rate is enhanced. Meanwhile, although different k would change the SoC balance speed, it would hardly bring a difference in  ${\rm SoC}_{\rm av}$ , indicating that changing k will not affect the overall efficiency of ESS.

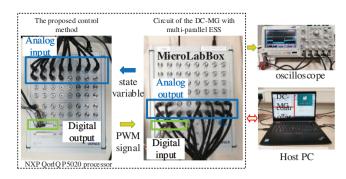

#### 6.2 | HIL experiment result

The dSPACE-based HIL platform is built, as shown in Figure 11, to verify the performance of the proposed inertia-emulation-based cooperative control strategy under different working conditions which include different operation modes (charging and discharging modes) and their switching, different power levels (light load and heavy load, i.e. changed operation points), the different levels of disturbance power, and the influences of control parameters. The DC-MG is built in the power electronics simulation software MATLAB and simulated by compact prototyping unit MicroLabBox with a time step of  $100~\mu s$ . The discrete control algorithm is implemented in the NXP QorlQ P5020 processor to generate the gate signals of all

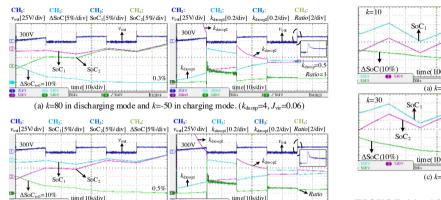

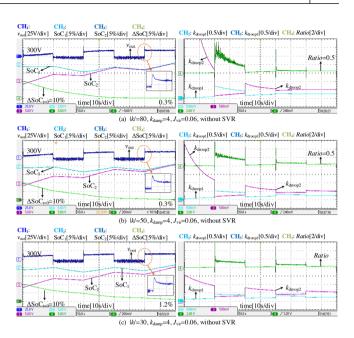

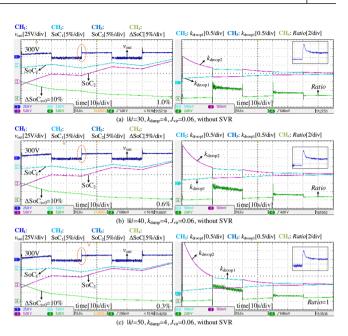

(a) Charging mode and k=80. ( $k_{damp}=4$ ,  $J_{vir}=0.06$ , without SVR)

(b) Discharging mode and k=-50. ( $k_{damp}=4$ ,  $J_{vir}=0.06$ , without SVR)

**FIGURE 12** The SoC balance in different mode, when  $SoC_{1, t=0} = 60\%$  and  $SoC_{2, t=0} = 50\%$

IGBTs and the sampling frequency is 10 kHz. The analog signals and digital signals (state variables and pulse width modulation (PWM) signals) are transferred through I/O interfaces and cables.

This dSPACE-based HIL experiment has the following advantages similar to physical experiment platform:

- Uncertain measurement disturbances in the HIL experiment (similar to sensors);

- 2. Unknown harmonics caused by capacitors or inductors of the signal transmission cables and MicroLabBox;

- 3. Digital signal processor, NXP QorlQ P5020, is adopted in this HIL experimental platform and the sampling frequency is 10 Hz. Its high performance, high-efficiency core and integration make it very well suited as a control processor.

- Considering time delay of discrete control, sampling and signal transmission.

Therefore, based on the above advantages similar to the whole physical experiment, this HIL experiment is sufficient to verify the theoretical analysis in this article.

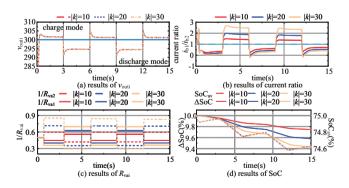

## 6.2.1 | Case *I*: Performance of the SoC self-balance algorithm in different operation modes of ESS

Case I validates the effectiveness of the SoC self-balance algorithm when ESS operates in different modes. And the current sharing coefficient  $k_{\text{droopi}} = 1/R_{\text{vai}}$  and current ratio between ESUs  $Ratio = i_{\text{s1}}/i_{\text{s2}}$  are defined.

In Figure 12a, ESS operates in charging mode with  $P_{\rm s} = 5$  kW and  $P_{\rm const} = 1$  kW, as well as k is selected as 80. In Figure 12b, ESS operates in discharging mode with  $P_{\rm s} = 5$  kW and  $P_{\rm const} = 6$  kW, and k is changed to -50. The initial SoCs of ESUs are 60% and 50%. It can be observed from Figure 12a that ESU<sub>1</sub> with a larger SoC is allocated less power than ESU<sub>2</sub> in the charging mode, because  $k_{\rm droop1}$  is smaller than  $k_{\rm droop2}$  and

(b) k=50 in discharging mode and k=-40 in charging mode. ( $k_{danno}=4$ ,  $J_{vir}=0.06$ )

(c) k=30 in discharging mode and k=-20 in charging mode. (k<sub>damp</sub>=4, J<sub>vir</sub>=0.06)

**FIGURE 13** The effect of k on the SoC balance speed, when SoC<sub>1, t=0</sub> = 60% and SoC<sub>2, t=0</sub> = 50% (without SVR)

the injected current is smaller. As a result,  $SoC_1$  and  $SoC_2$  tend to balance, and  $\Delta SoC_{12}$  drops from 10% to 0.3%. Finally, the delivered current and the current sharing coefficient of ESUs become equal (i.e. *Ratio* = 1).

On the other hand, it can be found from Figure 12b that  $ESU_1$  with a larger SoC delivers more power in the discharging mode due to that  $k_{\rm droop1}$  of  $ESU_1$  is larger than  $k_{\rm droop2}$ . Thus  $\Delta SoC_{12}$  converges from 10% to 0.6% and 1/*Ratio* gradually approaches 1. Therefore, the proposed SoC self-balance algorithm can maintain good performance in the dual-quadrant operation.

# 6.2.2 | Case *II*: Performance of the SoC self-balance algorithm with different *k* and sudden power fluctuation

In case II, the SoC balance effect of the proposed strategy in case of power fluctuation is validated and the influence of SoC equalization speed adjustment factor k on the convergence speed is investigated.  $P_{\rm s}$  is constant at 5 kW. The initial power of  $P_{\rm const}$  is 1 kW, which suddenly increases or decreases by 5 kW every 20 s to change the operation mode of ESS. The initial SoC of ESUs are 60% and 50%. The result is shown in Figure 13.  $k_{\rm droop1}$  of ESU<sub>1</sub> with a larger SoC is larger in discharge mode, and thus the output current is larger, while  $k_{\rm droop1}$  becomes smaller and the injected current is smaller in the charge mode. As a result,  $\Delta {\rm SoC}_{12}$  converges from 10% to 0.3% (i.e. the activation threshold), 0.8% and 1.36%, respectively, as shown in Figure 13. Note that, after  $\Delta {\rm SoC}_{12}$  is converged to 0.3%, the SoC self-balance algorithm will stop working, and ESUs will

**FIGURE 14** The effect of & on the SoC balance when  $SoC_1 = 80\%$  and  $SoC_2 = 70\%$

share the power according to the initial value of the droop coefficient  $R_{0 \text{ vai}}$ , that is,  $k_{\text{droopi}}$  is equal to 0.5 and the current ratio *Ratio* becomes 1, as shown in Figure 13a.

Hence, it can be concluded that the proposed SoC self-balance algorithm is still valid under varying load conditions and can realize the free switch between double-quadrant operations. Besides, it can be observed that faster dynamic power sharing equalization can be achieved with larger |k|, which obviously accelerates the SoC equalization speed. This is in accordance with the theoretical analysis.

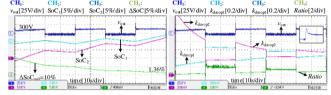

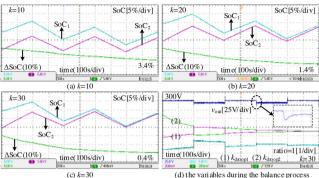

The experimental waveform with varying k is shown in Figure 14, when  $P_{\rm s}=3$  kW and  $P_{\rm const}=2$  kW.  $P_{\rm net}(=P_{\rm const}-P_{\rm s})$  is disturbed by 2 kW every 200 s and the operation mode of ESS is thus changed. The initial SoCs of these ESUs are 80% and 70%. In discharge mode,  $v_{\rm out}$  of ESU is lower than  $v_{\rm dcn}$ , and  $v_{\rm out}$  is higher than  $v_{\rm dcn}$  in charge mode, as shown in Figures 14a to 14c.  $k_{\rm droop1}$  of ESU<sub>1</sub> with a larger SoC is larger than  $k_{\rm droop2}$  in discharge mode, and thus the output current is larger. In the charge mode,  $k_{\rm droop1}$  of ESU<sub>1</sub> is smaller than  $k_{\rm droop2}$  and the injected current is smaller. As a result,  $\Delta {\rm SoC}_{12}$  converges to 0. From Figure 14, the final  $\Delta {\rm SoC}_{12}$  with a higher |k| becomes smaller after a same time period.  $\Delta {\rm SoC}_{12}$ ,  $v_{\rm total}=1000$  is 3.4%, 1.4% and 0.4% when |k| is 10, 20 and 30. The SoC equalization rate is enhanced by a higher |k|. These experiment results agree with those of the simulation.

It can be concluded by comparing Figures 13 and 14 that the SoC self-balance algorithm can achieve the dynamic SoC self-balance under varying loading conditions, different power disturbance conditions and various initial SoC of ESUs.

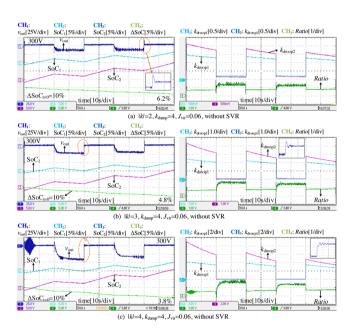

Moreover, the experimental waveform of three ESUs in parallel is shown in Figure 15.  $P_{\rm net}(=P_{\rm const}-P_{\rm s})$  is disturbed by 2 kW every 20 s and the operation mode of ESS is thus changed. The initial SoCs of these ESUs are 55%, 50% and 45%. Similar to the result in Figure 14 (two ESUs in parallel), the ESUs regulated by the proposed SoC self-balance algorithm also operate in the manner that the ESU with higher SoC should release more power in discharge mode and absorbless power in charge mode than the one with lower SoC. The SoC unbalance can be removed much faster when choosing a larger |k|.

**FIGURE 15** The effect of the SoC balance algorithm on multi-parallel ESUs when SoC<sub>1</sub> = 55%, SoC<sub>2</sub> = 50% and SoC<sub>3</sub> = 45%

# 6.2.3 | Case *III*: Performance of the proposed SoC self-balance algorithm for ESUs with different capacities

In case III, different ESU capacities condition is considered to test the SoC balance ability of the proposed SoC self-balance algorithm.  $P_{\rm s}$  is constant at 5 kW, and the initial value of  $P_{\rm const}$  is 1 kW which increases or decreases by 5 kW every 20 s to change the operation mode of ESS. The initial SoCs are 60% and 50%. The experimental results are shown in Figures 16 and 17. The rated capacities are selected as ESU<sub>1</sub> = 1.4 Ah and ESU<sub>2</sub> = 2.8 Ah in Figure 16, and ESU<sub>1</sub> = 2.8 Ah and ESU<sub>2</sub> = 1.4 Ah in Figure 17. Correspondingly, the initial value of the droop coefficient will be selected according to their capacities, that is,  $R_{0 \text{ val}}$  = 4 and  $R_{0 \text{ va2}}$  = 2 in Figure 16, and  $R_{0 \text{ val}}$  = 2 and  $R_{0 \text{ val}}$  = 4 in Figure 17.

It can be concluded from Figures 16 and 17 that the proposed SoC self-balance algorithm still can dynamically balance the SoC and eliminates the SoC difference although the ESUs capacities are different. And similarly, the  $\Delta \text{SoC}_{12}$  converges to 0 much faster with k increasing. After achieving SoC balance, the current ratio Ratio becomes 0.5 in Figure 16 ( $k_{\text{droop1}} = 0.25$  and  $k_{\text{droop2}} = 0.5$ ) and 2 in Figure 17 ( $k_{\text{droop1}} = 0.5$  and  $k_{\text{droop2}} = 0.25$ ), respectively, due to that the current is allocated according to the inverse proportion of the initial values of droop coefficients.

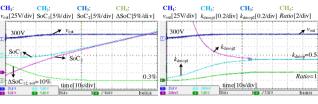

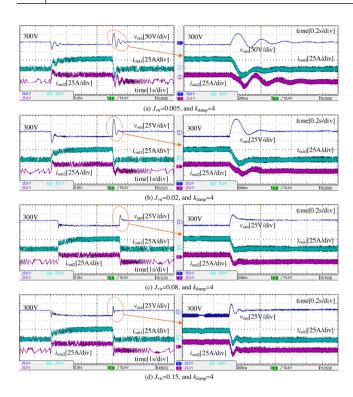

#### 6.2.4 | Case IV: Performance of IEL

Case IV verifies that the system stability has been significantly improved by the proposed inertia-emulation-based cooperative

**FIGURE 16** Performance of the SoC balance algorithm for  $ESU_1 = 1.4$  Ah and  $ESU_2 = 2.8$  Ah, when  $SoC_{1, t=0} = 60\%$  and  $SoC_{2, t=0} = 50\%$

**FIGURE 17** Performance of the SoC balance algorithm for  $ESU_1=2.8$  Ah and  $ESU_2=1.4$  Ah, when  $SoC_{1,\ t=0}=60\%$  and  $SoC_{2,\ t=0}=50\%$

control strategy while the SoC can be dynamically balanced.  $P_{\rm s}$  is constant at 3 kW, and the initial value of  $P_{\rm const}$  is 1 kW which increases or decreases by 5 kW every 4 s. Figures 18 and 19 present the waveform under varying control parameters.

It can be observed from Figure 18 that the IEL controlled Bi-C can be equivalent to a third-order system approximately and the dynamic process can be decomposed into a superposition of a first-order inertia component and an oscillation mode [22]. As  $J_{\rm vir}$  increases, the time constant of the inertia component gradually increases, indicating that the system inertia is enhanced.

**FIGURE 18** The influence of  $J_{vir}$ , when ignoring SVR loop

The influence of  $J_{\rm vir}$  on the oscillation mode is relatively complicated. The oscillation frequency of oscillation mode gradually increases with  $J_{\rm vir}$  increasing, and its oscillation amplitude is well suppressed first, and then increases (compare Figures 18c and 18d), implying that the damping increases first and then decreases. The experiment result of  $J_{\rm vir}$  is consistent with the analysis of Figure 6b.

With  $k_{\rm damp}$  increasing, a different trend from Figure 18 can be observed in Figure 19 [22]. As  $k_{\rm damp}$  increases, the time constant of the inertia component gradually decreases, indicating the reduced inertia. Also, the oscillation frequency of the oscillation mode gradually decreases. In addition, the oscillation amplitude of the oscillation mode first decreases (compare Figures 19a and 19b) and then gradually increases, indicating that the system damping first increases and then decreases. The experiment results of  $k_{\rm damp}$  agree with the analysis of Figure 6a.

#### 6.2.5 | Case V: Performance of SVR loop

Case V verifies the impact of SVR loop, as shown in Figure 20.  $P_{\rm s}$  is constant at 3 kW. The initial value of  $P_{\rm const}$  is 2 kW, which increases or decreases by 2 kW every 4 s. Comparing Figures 20a and 20b, SVR can eliminate steady-state error and ensure better voltage quality. In the transient process, SVR increases the oscillation amplitude, and as  $k_{\rm s}$  increases, the oscillation becomes more severe because of the interaction between SVR and IEL which form a second-order oscillation loop. Thus,  $k_{\rm s}$  should not be too large. In this article,  $k_{\rm s}=1$ .

**FIGURE 19** The influence of  $k_{\text{damp}}$ , when ignoring SVR loop. (a)  $k_{\text{damp}} = 1, J_{\text{vir}} = 0.06$ . (b)  $k_{\text{damp}} = 2, J_{\text{vir}} = 0.06$ . (c)  $k_{\text{damp}} = 4, J_{\text{vir}} = 0.06$ . (d)  $k_{\text{damp}} = 6, J_{\text{vir}} = 0.06$ . (e)  $k_{\text{damp}} = 8, J_{\text{vir}} = 0.06$ . (f)  $k_{\text{damp}} = 10, J_{\text{vir}} = 0.06$

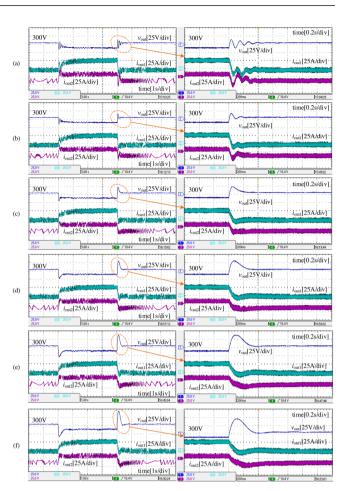

## 6.2.6 | Case VI: Comparison analysis with the double-quadrant SoC-based droop control method

In order to verify the superiority of the proposed inertia-emulation-based cooperative control strategy, it is compared with the double-quadrant SoC-based droop control method of [19, 20]. Note that the control effect of IEL has been compared with the traditional droop control and verified by simulation; thus, only the performance of SoC self-balance algorithm is compared with [19, 20] when the IEL is added into the method of [19, 20] for a fair comparison.  $P_{\rm s}$  is constant at 5 kW. The initial value of  $P_{\rm const}$  is 1 kW, which increases or decreases by 5 kW every 20 s. The initial SoCs of ESUs are 60% and 50%. The HIL experiment results of these two methods are shown in Figures 21 and 22. It can be concluded that the proposed method can balance the SoC more quickly under the condition of ensuring a smaller voltage deviation.

It can be seen from Figure 21 that although the convergence rate of SoC can be sped up by increasing k, a larger k will also lead to a larger steady-state voltage deviation with the double-quadrant SoC-based droop control method. By contrast, it can be observed from Figure 22 that the proposed SoC self-balance algorithm can not only improve the system

FIGURE 20 The influence of SVR loop

**FIGURE 21** Performance of the double-quadrant SoC-based droop control method of [13, 14]

stability, but also realize the dynamic balance of SoC among ESUs faster under the requirement of a smaller steady-state voltage deviation, indicating obvious advantages compared with the double-quadrant SoC-based droop control method. Different from [19, 20], the SoC can be converged more quickly by the proposed inertia-emulation-based cooperative control strategy with a smaller steady-state voltage deviation. Besides,

**FIGURE 22** Performance of the proposed inertia-emulation-based cooperative control strategy

the SVR loop can be activated to achieve secondary voltage recovery, when a larger value of k, which might cause a larger voltage deviation, is necessary to balance the SoC quickly. The combination of SoC balance, secondary voltage management and dynamic stability improvement is realized by the proposed inertia-emulation-based cooperative control strategy.

#### 7 | CONCLUSION

An inertia-emulation-based cooperative control strategy is proposed to address the SoC imbalance and voltage deviation problem during steady-state operation and the voltage stability problem caused by inertia-less in the transient process in multi-parallel ESS of DC-MGs, which includes SoC self-balance algorithm, IEL, and virtual-inductor-based SVR loop. Different from previous work, the combination of SoC balance and inertia enhancement is realized, the contradiction between SoC balance speed and system stability is solved and the corresponding optimal parameter selection method is given in this paper.

Specifically, SoC mismatch degree is defined and the power distribution is regulated by integrating this SoC mismatch degree into virtual droop resistance to achieve dynamic SoC balance. Thus, the contradiction between SoC balancing speed and maintaining system stability is addressed by this redefined SoC-based droop resistance function. The SoC convergence speed depends on the introduced adjustment factor k. Besides, IEL and SVR loop are developed based on DC motor model and circuit equivalence of inductors, respectively, to improve the dynamic stability and eliminate the steady-state voltage error. The dynamic performance analysis demonstrates that the larger exponent |k| accelerates balance speed. Moreover, SoC self-balance algorithm is a second-order system and the IEL can be simplified to a third-order system. Thus, appropriate  $J_{\rm vir}$  and

$D_{\rm d}$  could be selected based on the requirements of  $\xi$  and  $T_{\rm iner}$ . The steady region of k is discussed considering the boundaries of various constraints estimation, and the parameter optimal design process is presented.

To validate the correctness of the theoretical analysis, simulation and dSPACE-based HIL experiment are conducted under various working conditions, including different operation modes of ESS and their switching, different power levels (i.e. different operation points), the different levels of disturbance power, and the influences of control parameters. It is demonstrated that fast SoC balance, inertia effect and stiffness can be simultaneously ensured in multi-parallel ESS with the proposed method.

#### NOMENCLATURE

Subscript 'i' the ESU identifier index, i = 1, 2, 3,...

EV electric vehicle

SoC state-of-charge

ESU energy storage unit

ESS energy storage system

Bi-C bidirectional DC converter

VIC virtual inertia control

SVR secondary voltage recovery

IEL inertia emulation loop

$v_{\rm in}$  and  $v_{\rm out}$  input and output voltage of Bi-C

$d_i$  duty cycle of *i*th Bi-C

$i_{\rm b}$  and  $i_{\rm out}$  input and output current of Bi-C

$v_{\rm dcn}$  the rated value of  $v_{\rm out}$

$P_{\text{net}}$  net power of load subsystem (Zone II)

$L_{\rm s}$  ( $R_{\rm s}$ ) filter inductance and its resistor of Bi-C

C<sub>out</sub> output capacitor of Bi-C

$\Delta SoC_{ii}$  SoC difference between *i*th and *j*th ESU

$R_{\text{vai}}$  ( $R_{\text{va}}$ ) SoC-integrated droop resistance of *i*th Bi-C

$U_0$  and E input voltage and armature winding induced

potential of motor

$i_{\text{ref out}}$  reference value of  $i_{\text{out}}$

$R_{0 \text{ vai}}$  the initial value of  $R_{\text{vai}}$

$R_a$  armature winding resistance of DC motor

$R_{\rm rs}$  speed regulating resistance

$R_a$  armature winding resistance of DC motor

$\omega$  ( $\omega_{\text{vir}}$ ) angular velocity of (virtual) rotor

$C_{\text{Tm}}$  ( $C_{\text{T}}$ ) (virtual) torque coefficient

$\psi_{\rm m} \left( \psi \right)$  (virtual) magnetic flux

$T_{\rm m}$  ( $P_{\rm m}$ ) load torque (related electrical power)

$J_{\rm vir}$  virtual inertia coefficient of IEL

$D_{\rm d}$  virtual damping coefficient of IEL

k<sub>s</sub> stiffness coefficient of IEL

kSoC SoCequalization speed adjustment factor

$\lambda_i$  time-varying parameter indicating the SoC mismatch degree

$C_{\rm vir}$  virtual capacitor of IEL

$L_{\rm syr}$  virtual inductor of IEL

$i_{\rm vd}$  virtual damping current of IEL

$i_{\text{viner}}$  virtual inertia current of IEL

$i_{\text{syr}}$  virtual inductor current of IEL

' $\Delta$ ' the small-signal components

$\Delta v$  the voltage deviation from the rated value

#### **ACKNOWLEDGEMENTS**

This work is supported in part by China Scholarship Council (No. 201906130196).

#### CONFLICT OF INTEREST

We declare that we have no financial and personal relationships with other people or organizations that can inappropriately influence our work, there is no professional or other personal interest of any nature or kind in any product, service and/or company that could be construed as influencing the position presented in, or the review of, the manuscript entitled, 'An Inertia-Emulation based Cooperative Control Strategy and Parameters Design for Multi-parallel ESS in Islanded DC-MG'.

#### DATA AVAILABILITY STATEMENT

Data sharing not applicable to this article as no datasets were generated or analysed during the current study.

#### ORCID

Gang Lin https://orcid.org/0000-0002-5214-6891

#### REFERENCES

- Khorsandi, A., Ashourloo, M., Mokhtari, H.: A decentralized control method for a low-voltage DC microgrid. IEEE Trans. Energy Convers. 29(4), 793–801 (2014)

- Dragičević, T., et al: DC microgrids—Part I: A review of control strategies and stabilization techniques. IEEE Trans. Power Electron. 31(7), 4876– 4891 (2016)

- Fang, J., et al.: On the inertia of future more-electronics power systems. IEEE J. Emerg. Sel. Topics Power Electron. 7(4), 2130–2146 (2019)

- Samanta, S., Mishra, J.P., Roy, B.K.: Virtual DC machine: An inertia emulation and control technique for a bidirectional DC–DC converter in a DC microgrid. IET Electr. Power Appl. 12(6), 874–884 (2018)

- Oliveira, T.R., Gonçalves Silva, W.W.A., Donoso-Garcia, P.F.: Distributed secondary level control for energy storage management in DC microgrids. IEEE Trans. Smart Grid 8(6), 2597–2607 (2017)

- Fang, J., et al: An improved virtual inertia control for three-phase voltage source converters connected to a weak grid. IEEE Trans. Power Electron. 34(9), 8660–8670 (2019)

- Wu, W., et al.: A virtual inertia control strategy for DC microgrids analogized with virtual synchronous machines. IEEE Trans. Ind. Electron. 64(7), 6005–6016 (2017)

- Li, C., et al.: Virtual synchronous generator control for damping DCside resonance of VSC-MTDC system. IEEE J. Emerg. Sel. Topics Power Electron. 6(3), 1054–1064 (2018)

- Zhu, X., et al.: An inertia and damping control method of DC-DC converter in DC microgrids. IEEE Trans. Energy Convers. 35(2), 799–807 (2020)

- Wang, Y., et al.: Adjustable inertial response from the converter with adaptive droop control in DC grids. IEEE Trans. Smart Grid 10(3), 3198–3209 (2019)

- Yang, Y., et al.: Virtual inertia control strategy for improving damping performance of DC microgrid with negative feedback effect. IEEE J. Emerg. Sel. Topics Power Electron. 9, 1241–1257. https://doi.org/10. 1109/JESTPE.2020.2998812

- Zhi, N., et al.: An SOC-based virtual DC machine control for distributed storage systems in DC microgrids. IEEE Trans. Energy Convers. 35(3), 1411–1420 (2020)

Lin, G., et al.: A virtual inertia and damping control to suppress voltage oscillation in Islanded DC microgrid. IEEE Trans. Energy Convers. 36(3), 1711–1721 (2021)

- Li, Y., et al.: Flexible voltage control strategy considering distributed energy storages for DC distribution network. IEEE Trans. Smart Grid 10(1), 163– 172 (2019)

- Huang, W., Abu Qahouq, J.A.: Energy sharing control scheme for Stateof-Charge balancing of distributed battery energy storage system. IEEE Trans. Ind. Electron. 62(5), 2764

–2776 (2015)

- Cao, Y., Abu Qahouq, J.A.: Hierarchical SOC balancing controller for battery energy storage system. IEEE Ind. Electron. 68(10), 9386–9397 (2021)

- Bi, K., et al.: Active SOC balancing control strategy for modular multilevel super capacitor energy storage system. IEEE Trans. Power Electron. 34(5), 4981–4992 (2019)

- Hoang, K.D., Lee, H.: Accurate power sharing with balanced battery state of charge in distributed DC microgrid. IEEE Trans. Ind. Electron. 66(3), 1883–1893 (2019)

- Lu, X., et al.: State-of-charge balance using adaptive droop control for distributed energy storage systems in DC microgrid applications. IEEE Trans. Ind. Electron. 61(6), 2804–2815 (2014)

- Lu, X., et al.: Double-quadrant state-of-charge-based droop control method for distributed energy storage systems in autonomous DC microgrids. IEEE Trans. Smart Grid 6(1), 147–157 (2015)

- Zhang, C., et al.: Robust and adaptive estimation of state of charge for lithium-ion batteries. IEEE Trans. Ind. Electron. 62(8), 4948–4957 (2015)

- Lin, G., et al.: Comparative analysis on the stability mechanism of droop control and VID control in DC microgrid. Chinese J. Electr. Eng. 7(1), 37–46 (2021) https://doi.org/10.23919/CJEE.2021.000003

- Zhang, Y., et al.: Coordinated control of networked AC/DC microgrids with adaptive virtual inertia and governor-gain for stability enhancement. IEEE Trans. Energy Conversion. 36(1), 95–110 (2021)

- Zhi, N., et al.: Power-loop-free virtual DC machine control with differential compensation. IEEE Trans. Ind. Appl. 58(1), 413–422 (2022)

- Lin, G., et al.: Low-frequency oscillation analysis of virtual-inertiacontrolled DC microgrids based on multi-timescale impedance model. IEEE Trans. Sustain. Energy 13(3), 1536–1552 (2022)

- Bi, K., et al.: An improved SOC balancing strategy for HVDC modular energy storage system based on low bandwidth communication with enhanced current regulation accuracy. IEEE Trans. Energy Convers. 36(4), 3355–3364 (2021)

- Han, H., et al.: A local-distributed and global-decentralized SoC balancing method for hybrid series-parallel energy storage system. IEEE Syst. J. 16(2), 2289–2299 (2022)

- Chowdhury, S., Shaheed, M.N.B., Sozer, Y.: State-of-charge balancing control for modular battery system with output DC bus regulation. IEEE Trans. Transp. Electrification 7(4), 2181–2193 (2021)

- Xia, Z., Abu Qahouq, J.A.: State-of-charge balancing of lithium-ion batteries with state-of-health awareness capability. IEEE Trans. Ind. Appl. 57(1), 673–684 (2021)

How to cite this article: Lin, G., Liu, J., Zhou, Y., Li, Y., Rehtanz, C., Wang, S., Wang, P., Zuo, W.: An inertia-emulation-based cooperative control strategy and parameters design for multi-parallel energy storage system in islanded DC microgrids. IET Gener. Transm. Distrib. 16, 4370–4385 (2022).

https://doi.org/10.1049/gtd2.12605